You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

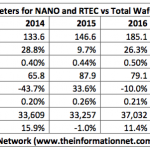

On June 24, 2019, Nanometrics and Rudolph Technology announced they will combine in an all-stock merger of equals transaction. The companies say the combination increases the SAM (served available market) opportunity to approximately $3B.

This article attempts to analyze the two companies in their different business segments,… Read More

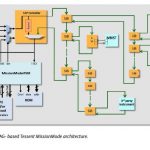

It’s easy to imagine that the main impetus for automotive electronics safety standards like ISO 26262 is the emergence of autonomous driving technology. However, even cars that do not offer this capability rely heavily on electronics for many critical systems. These include engine control, braking, crash sensors, and stability… Read More

The rising complexity of modern SoC designs, as enabled by progressing manufacturing technology, leads to an increasing validation challenge as the only way to manage complexity increase is by re-using more pre-designed IP blocks. These IP-blocks are provided by various suppliers such as a foundry partner, internal design… Read More

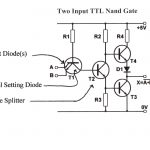

The “20 Questions with John East” series continues

Most people in the IC business understand very well that TTL products dominated our industry for 30 years or so. They’ll also probably know that TI was the king of TTL. But, if you ask those people what TTL is, most won’t have any idea. If you’re one of those people, rest easy. … Read More

The Silence hacking crew, mostly attributed to a group of very crafty Russian hackers, has struck again pulling-in over $3 million in cash from ATMs.

At least 3 banks have been attacked in the latest campaign, with Dutch Bangla Bank being the largest. The criminal hackers first compromised the bank’s card management infrastructure… Read More

Figure 1 is the most basic of all the predictable parameters of the semiconductor industry, even more so than Moore’s Law. It is the learning curve for the transistor. Since 1954, the revenue per transistor (and presumably the cost per transistor, if we had the data from the manufacturers) has followed a highly predictable learning… Read More

The automotive industry is a funny business. It is simultaneously ruled by ego driven “visionaries” and penny-pinching bean counters. (Don’t believe me? Just ask Bob Lutz.) This id-superego tension plays out in business section headlines every day most recently including the death of FCA’s Sergio… Read More

In the semiconductor world when we hear “full-stack” we think of a chip, chipset or board with a bunch of software, which can be connected to sensors of various types on one end, trained networks in the middle and actuators on the other side. But of course that’s not really a full-stack. The real thing would be deployment of an entire… Read More

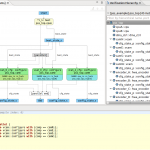

I first connected with Gerhard Angst of Concept Engineering over 15 years ago, because I was using their SpiceVision PRO tool to visual SPICE netlists received from customer designs to be debugged in a FastSPICE circuit simulator. The ability to visualize a transistor-level netlist was simply essential to quickly understanding… Read More

Portable stimulus has been a hot topic for a couple of years in the EDA and semiconductor industries. Many observers see this approach as the next major advance in verification beyond the Universal Verification Methodology (UVM), and the next step higher in abstraction for specifying verification intent. The basic idea is to … Read More

Solving the EDA tool fragmentation crisis