The device roadmap for the next few advanced process nodes seems relatively clear. The FinFET topology will subsequently be displaced by a “gate-all-around” device, typically using multiple stacked channels with a metal gate completely surrounding the “nanosheets”. Whereas the fin demonstrates improved gate-to-channel… Read More

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More

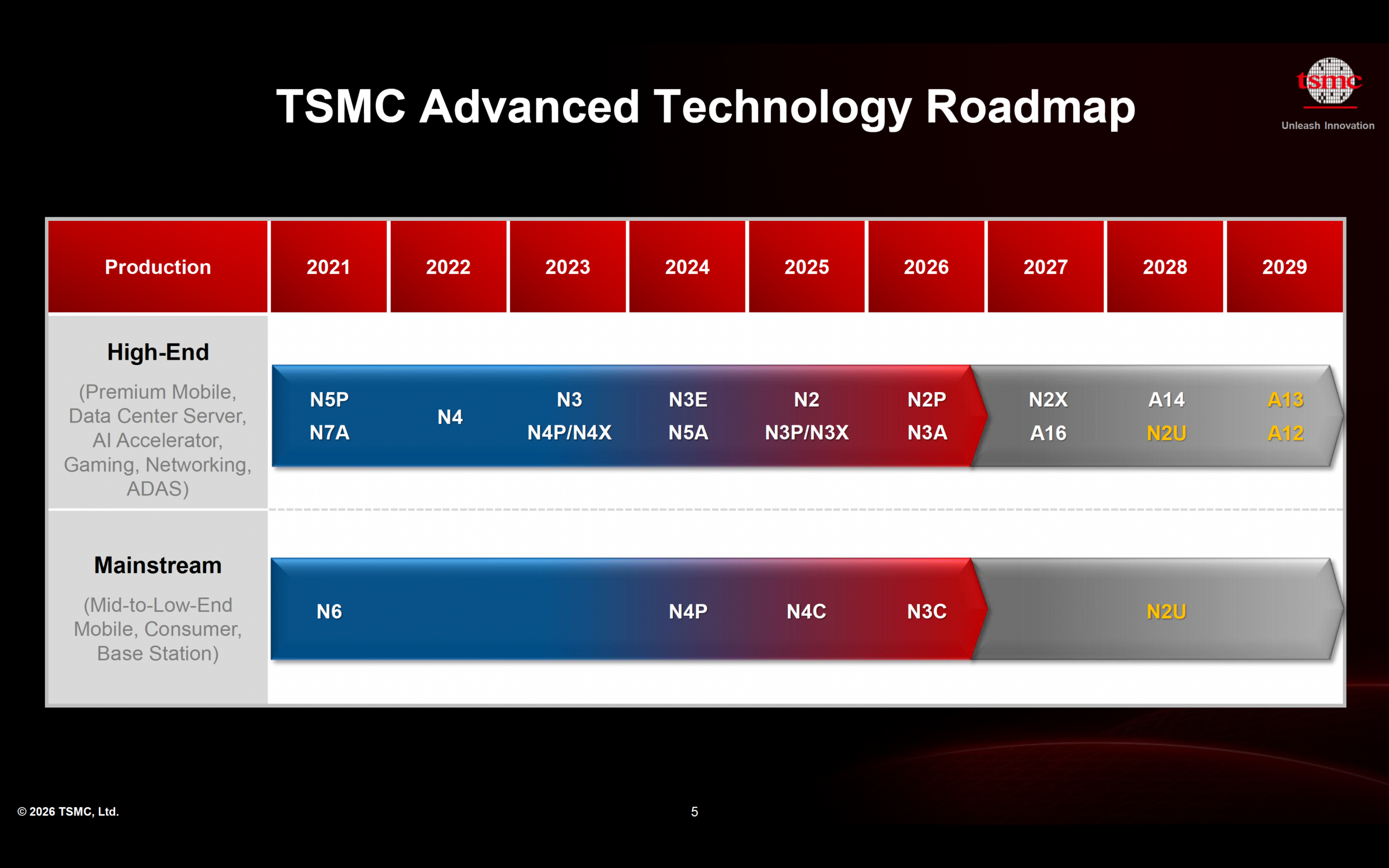

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More

The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

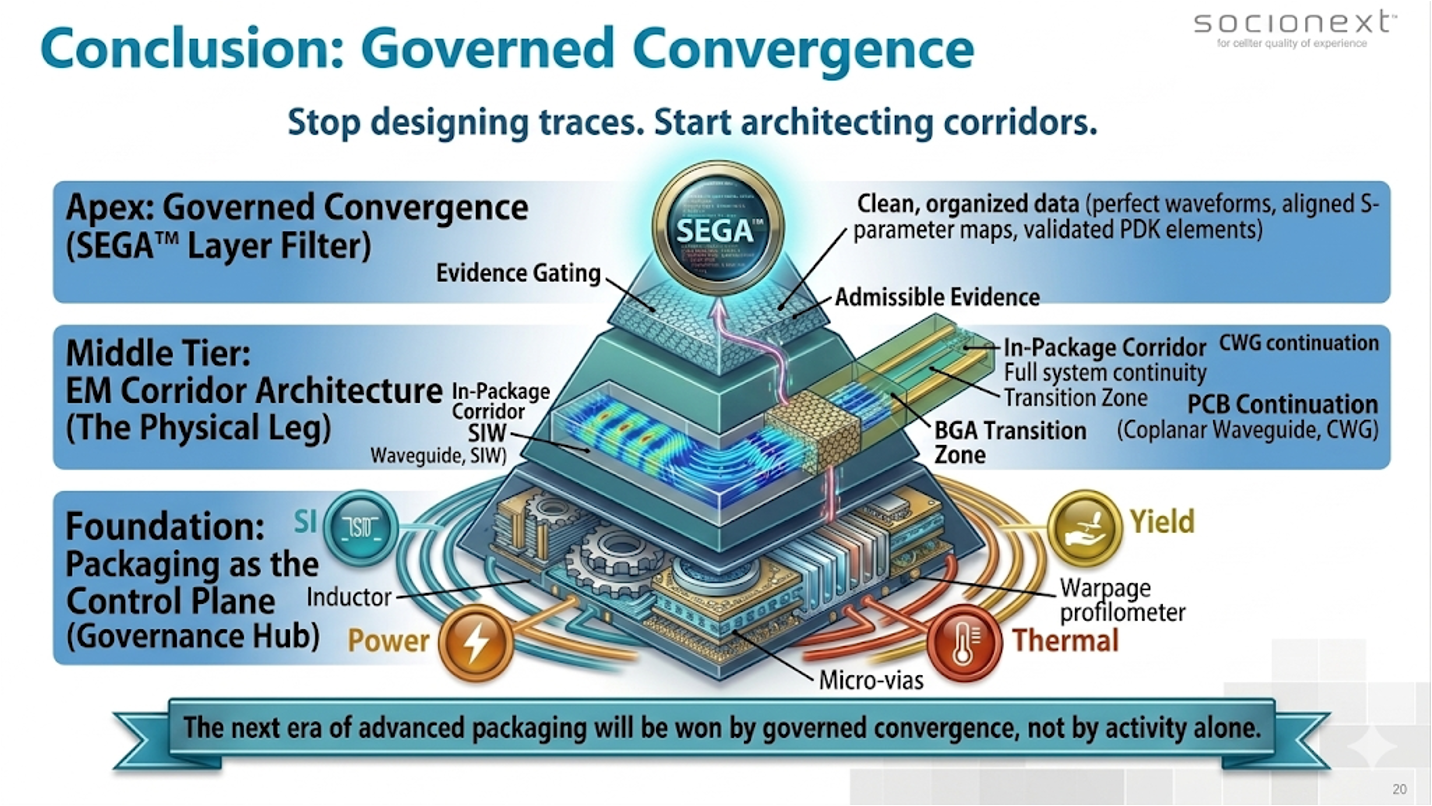

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read MoreTesla’s Musk Mocks Marketing

The Automotive News had a standout year in 2020 – thriving at a time when many publishers suffered. With factories and dealerships shuttered in the spring due to the pandemic, the outlook was bleak but the Automotive News dug in amplifying its reporting with multiple podcasts and video content documenting the ups and downs

Amazon Tesla Uber and DoorDash

As the death toll in the U.S. from COVID-19 approaches 300,000 I am impressed by the resilience of pandemic doubters and deniers. I’m talking about the point-three-percent-ers* who have shifted from calling COVID-19 a hoax to encouraging as many people as possible to get the virus to “get it over with.”

Maybe “impressed” isn’t… Read More

Analog Bits is Taking the Virtual Holiday Party up a Notch or Two

As 2020 comes to a close, I hear a lot of chatter about virtual meeting fatigue; “I’m Zoomed out”. We’ve all attended virtual versions of conferences this year with various degrees of success. Overall, I have to say these events are getting better. Semiconductor and EDA folks have a way of adapting and inventing, and it’s showing … Read More

TrueChip CXL Verification IP

TrueChip is a Verification IP specialist. For more than 10 years they have provided verification IP’s, like USB, PCIe, Ethernet, Memory, AMBA, Display RISC V and many more. They have an extensive portfolio including a very interesting product that is “TruEYE™️ GUI” which is a debugger helper tool for the verifications IPs.

Protocol

… Read MoreMulticore System-on-Chip (SoC) – Now What?

A quick Q&A with Jeff Hancock, senior product manager for Mentor Embedded Platform Solutions, Siemens Digital Industries Software. Jeff oversees the Nucleus® real-time operating system (RTOS) and Mentor Embedded Hypervisor runtime product lines, as well as associated middleware and professional services. Over the… Read More

NetApp’s FlexGroup Volumes – A Game Changer for EDA Workflows

In my prior post on NetApp, I discussed how the company’s FlexCache technology can keep distributed design teams in sync. Coordination and collaboration are critical elements of any complex design project. The ability to deliver results quickly while managing the massive amounts of data is also a critical element of success.… Read More

Automatic Generation of SoC Verification Testbench and Tests

Last month, I blogged about a webinar on embedded systems development presented by Agnisys CEO and founder Anupam Bakshi. I liked the way that he linked their various tools into a common flow that spans hardware, software, design, verification, validation, and documentation. Initially I was rather focused on the design aspects… Read More

A Research Update on Carbon Nanotube Fabrication

It is quite amazing that silicon-based devices have been the foundation of our industry for over 60 years, as it was clear that the initial germanium-based devices would be difficult to integrate at a larger scale. (GaAs devices have also developed a unique microelectronics market segment.) More recently, it is also rather … Read More

The Heart of Trust in the Cloud. Hardware Security IP

You might think that cloud services run on never-ending racks of servers and switches in giant datacenters. But what they really run on is trust. Trust that your data (or your client’s data) is absolutely tamper-proof inside that datacenter. Significantly more secure than it would be if you tried to manage the same operations in… Read More

Solving the EDA tool fragmentation crisis