Engineers love to optimize their designs, but that implies that there are models and stimulus to automate the process. Process engineers have TCAD tools, circuit designers have SPICE for circuit simulation, logic designers have gate-level simulators, RTL designers use logic simulation, but what is there for the system architects… Read More

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

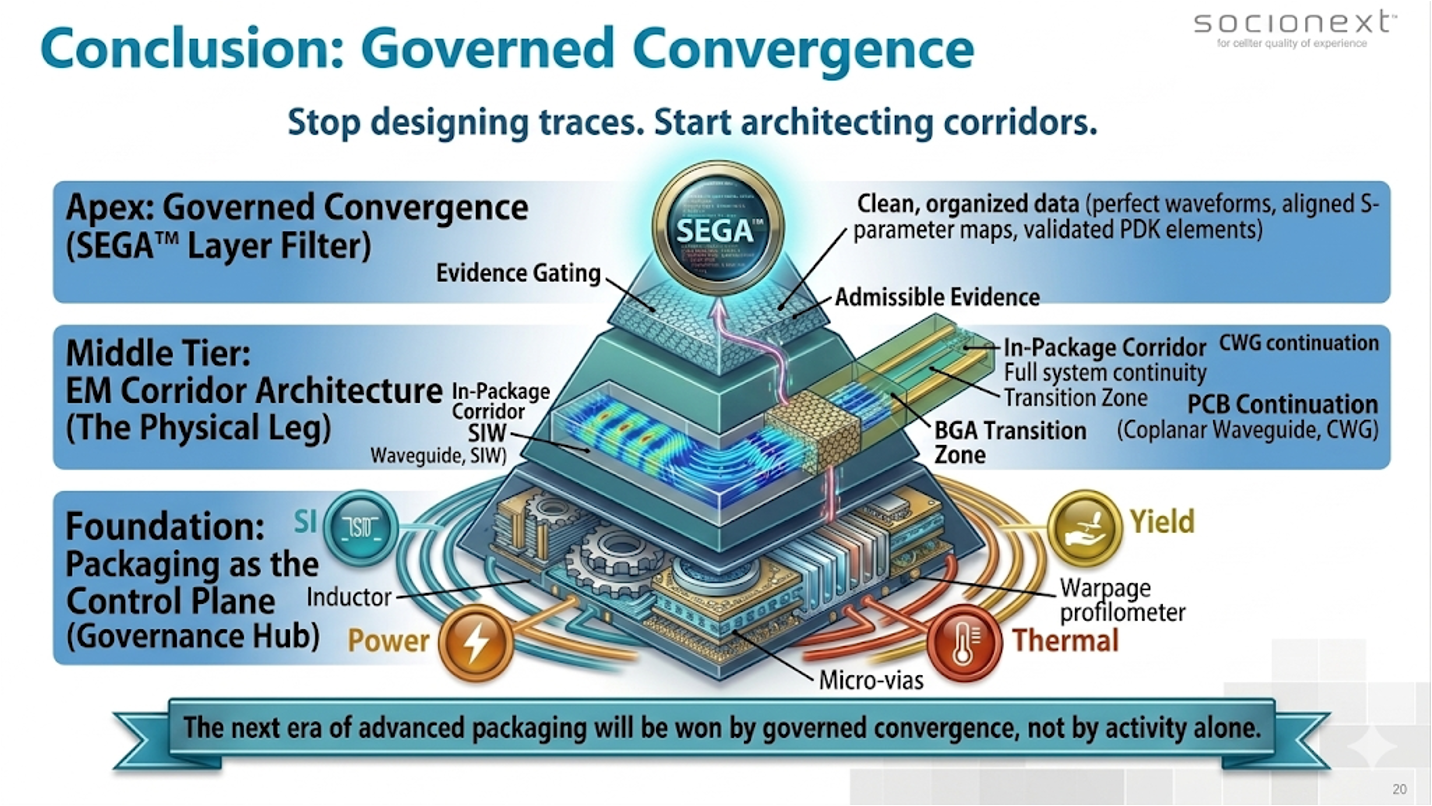

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read MoreSamtec Keynote – Power Integrity is the New Black Magic

The Signal Integrity Journal recently held a half day Electronic Systems SI/PI Forum that included presentations from industry leaders covering key design topics for signal integrity and power integrity engineers. The event was sponsored by Cadence. The keynote for the event was presented by Istvan Novak, principal signal… Read More

Mars Perseverance Rover Features First Zoom Lens in Deep Space

On July 30, 2020, NASA launched the Mars 2020 Perseverance rover, which is scheduled to land today. Perseverance has been deployed to Mars with a new mission: to search for evidence of past life and collect samples that will eventually be brought back to Earth by future missions.

Is IBM’s 2nm Announcement Actually a 2nm Node?

IBM has announced the development of a 2nm process.

IBM Announcement

What was announced:

- “2nm”

- 50 billion transistors in a “thumbnail” sized area later disclosed to be 150mm2 = 333 million transistors per millimeter (MTx/mm2).

- 44nm Contacted Poly Pitch (CPP) with 12nm gate length.

- Gate All Around (GAA), there are several ways

Podcast EP19: The Emergence of 2.5D and Chiplets in AI-Based Applications

Dan and Mike are joined by Sudhir Mallya, vice president of corporate and product marketing at OpenFive. We explore 2.5D design and the role chiplets play. Current technical and business challenges are discussed as well as an assessment of how the chiplet market will develop and what impact it will have.

The views, thoughts, and

CEO Interview: Srinath Anantharaman of Cliosoft

Srinath Anantharaman founded Cliosoft in 1997 and serves as the company’s CEO. He has over 40 years of software engineering and management experience in the EDA industry. Srinath graduated with a Bachelor of Technology from IIT/Kanpur and MSEE from Washington University in St. Louis.

The last time we talked to you was 2017. … Read More

Verification Management the Synopsys Way

Remember the days when verification meant running a simulator with directed tests? (Back then we just called them tests.) Then came static and formal verification, simulation running in farms, emulation and FPGA prototyping. We now have UVM, constrained random testing and many different test objectives (functional, power,… Read More

Spot-On Dead Reckoning for Indoor Autonomous Robots

One meaning of the word “reckoning” says it is the action or process of calculating or estimating something. But dead reckoning? What does that mean? Believe it or not, we have all deployed dead reckoning to varying degrees of success on different occasions. As an example, when driving on a multi-lane winding highway and direct … Read More

Why Near-Threshold Voltage is an Excellent Choice for Hearables

In the previous blogs on this topic, we’ve seen that utilizing near-threshold voltage (NTV) saves incredible amounts of energy, theoretically up to 10x and in practice from 2x to 4x. But there is a price which makes some applications more suited for NTV than others. This is due to the inevitable performance (speed) loss of NTV as … Read More

Transistor-Level Static Checking for Better Performance and Reliability

My first transistor-level IC design job was with Intel, doing DRAM designs by shrinking the layout to a smaller process node, and it also required running lots of SPICE runs with manually extracted parasitics to verify that everything was operating OK, meeting the access time specifications and power requirements across PVT … Read More

Solving the EDA tool fragmentation crisis