Just as SmartTV has become a household term, SmartDV has become a well-known name within semiconductor design and verification circles. SmartDV™ Technologies is the proven and trusted choice for Smart Design IP and a range of Verification Solutions™ from Verification IP, including assertion-based and post-silicon validation IP, to synthesizable transactors and memory models. Top semiconductor companies and electronics OEM companies are among SmartDV’s customers. If you don’t already know about SmartDV, you soon will.

I was very curious to get insights into their key strengths and differentiators enabling their success in the marketplace. Why are 7 out of the top 10 semiconductor companies and 4 of the world’s largest consumer electronics companies SmartDV’s direct customers? SmartDV grew their revenue more than 50% in 2020 and is on pace to have a record 2021. What is behind their rapid revenue growth and customer engagements?

I went to task, when I got an opportunity to interview Bipul Talukdar, SmartDV’s director of applications engineering for North America. Bipul was very transparent and provided great insights into what has enabled them to become the market leader in the VIP space and a fast-growing leader in the Design IP space. This blog is a synthesis of that interview discussion.

Expansion of SmartDV’s Mission

When the company was founded in 2007, their mission was focused on VIP. With their proprietary compiler technology and methodology, and other key strengths and differentiators, they quickly grew to market leadership position. During this journey, they observed their ability to accelerate delivery of Design IP as well. So, the company has expanded their mission to include Design IP. Their vision is to continue to maintain their VIP market leadership and earn a leadership position in the Design IP.

Ideal Attributes of IP Solutions

An ideal IP solution is one that is scalable, portable and customizable. Once we have these, the design and verification tasks are matters of process and execution by the chip development and validation engineers.

Portability

The design process starts with architecture exploration and goes through various stages from hardware description language (HDL), to gate level netlist, to layout and tapeout, on to silicon and post-silicon validation. At each stage, the design needs to be verified to ensure it is still meeting the intent as per the design requirement specs. There are various verification platforms used at each stage. These VIP solutions need to port seamlessly across the various stages. This is a big challenge.

In the context of Design IP, portability refers to the ability to be able to use an IP across different process nodes.

Scalability

As “design changes” increase or decrease complexity, the VIP solutions need to be able to scale accordingly and quickly. If the same verification solution is used independent of “design changes”, there will either be a bottleneck in terms of performance or the solution will become inadequate, making it impossible to verify the design.

In the context of Design IP, scalability refers to the ability to quickly enhance or downgrade a design in terms of performance or power.

Customizability

If a design is tweaked, and the VIP is not modified, unnecessary space may be taken in the FPGA prototyping solution or on the hardware emulator. So, the speed at which a verification solution can be customized is an important attribute of the VIP solution itself.

In the context of Design IP, customizability refers to the ability to quickly tweak a design to add, remove or modify features or functionality.

SmartDV’s Proprietary SmartCompiler Technology

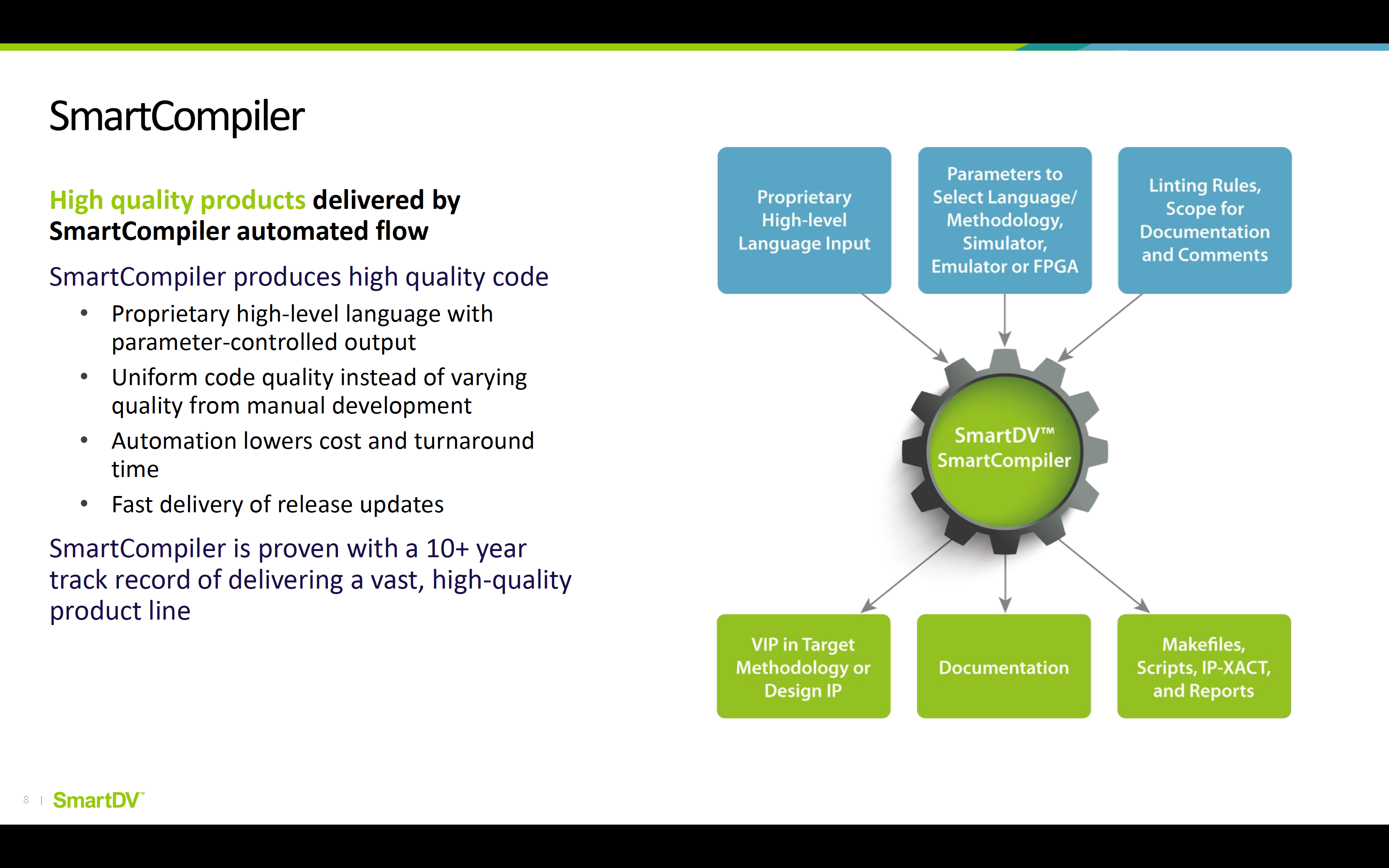

This is a key asset that has been developed and perfected by SmartDV over the years and provides a huge advantage to them. Refer to figure below. The SmartCompiler takes input in the form of a proprietary high-level language. The choice of design specification language, methodology, verification platform, etc., are specified in parameterized form. Standardized Linting rules built into the compiler ensure that variations in input style due to individual development engineer’s style are homogenized. The SmartCompiler technology eliminates the need to play with low-level specification and is able to quickly generate Design IP solutions and VIP solutions. These proprietary compilers, which are for internal use, have enabled SmartDV to get their IP solutions to the market, well ahead of others.

There are two different divisions within SmartDV, one for VIP and the other for Design IP. And there are two different compilers, one for generating VIP and another for generating Design IP. And these two compilers do not reuse or share any code.

SmartDV’s IP Solutions

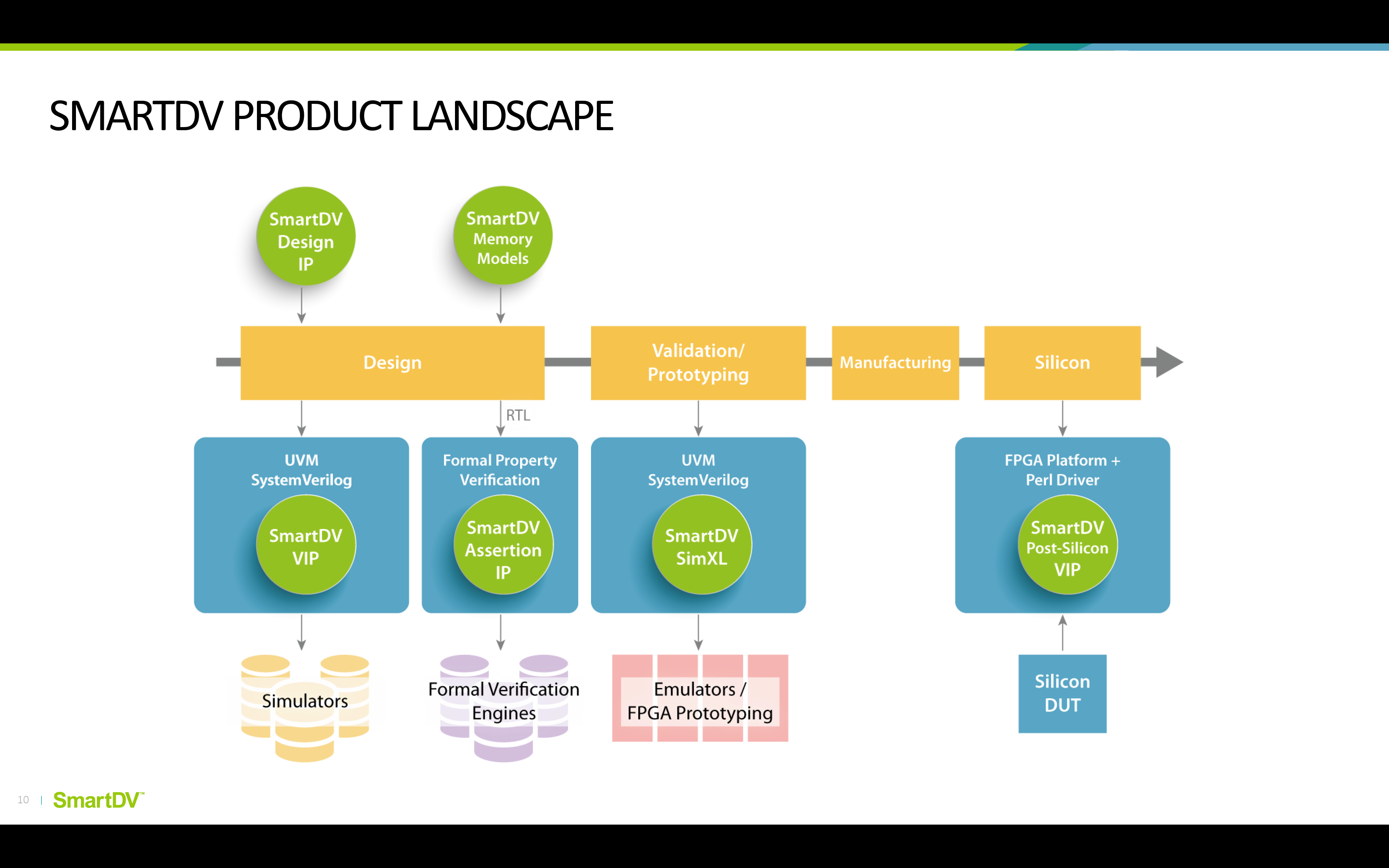

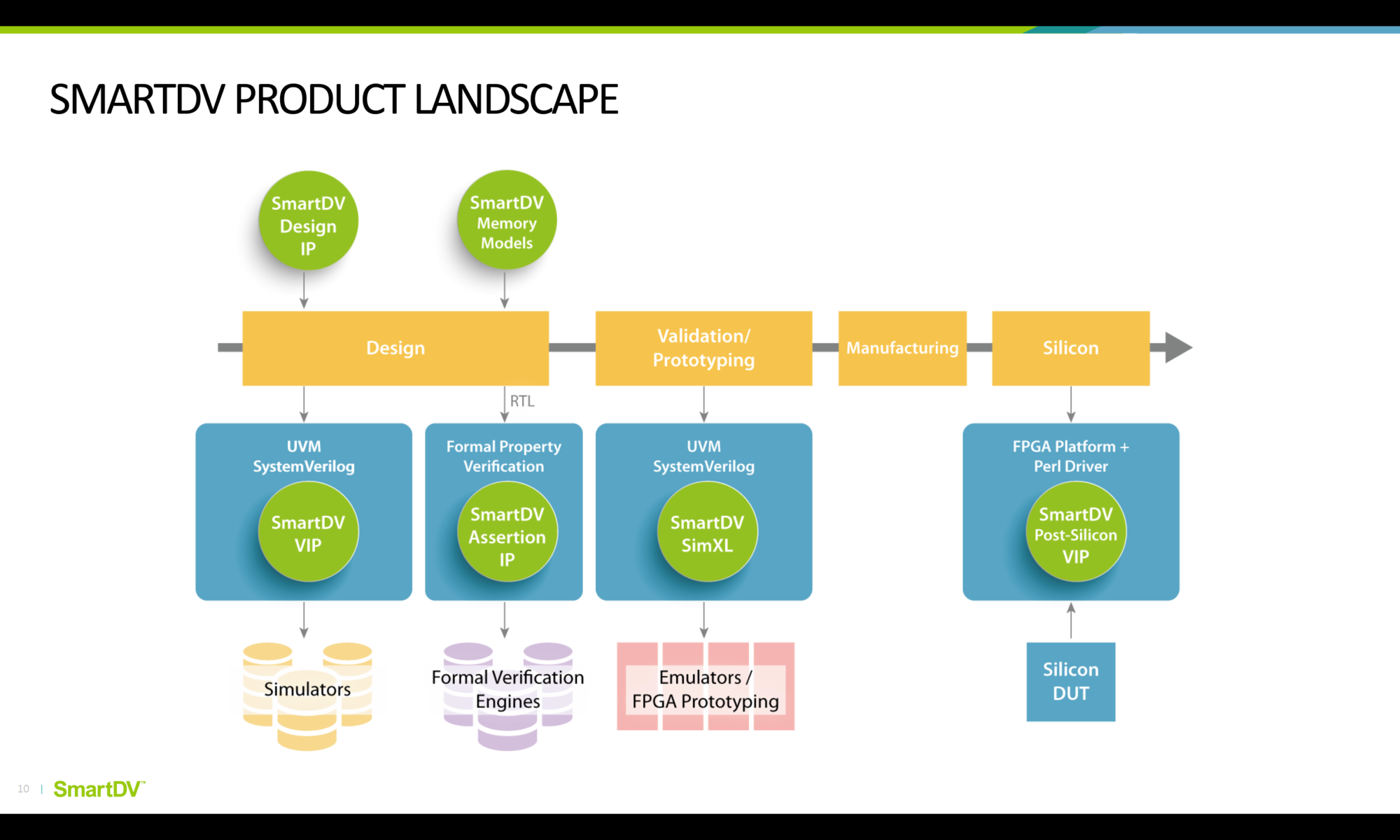

SmartDV currently offers 600 different Design and VIP solutions. That is an impressive array of IP solutions. Refer to the figure below for the extensiveness of their IP solutions covering the entire chip development lifecycle.

The SmartDV SmartCompiler technologies make their IP solutions easily scalable and rapidly customizable. As for portability, see below.

VIP Solutions

SmartDV’s verification solutions follow a modular architecture and consists of three layers. One is the hardware component that can run on an emulator or FPGA prototyping platform, one is software component that can run on a Linux machine and the third is the communication layer between these two. Because of this architecture and design, their VIP solutions are seamlessly portable.

Design IP Solutions

SmartDV’s IP are offered in high-level language form and thus are automatically portable.

The SmartDV Difference

Productivity/Turn-Around-Time

SmartDV is usually able to deliver new IP first to the market. They are able to develop a VIP solution from scratch with just 50% of the effort compared to others. And for developing subsequent platforms of the same IP, it takes just 25% of the effort compared to others. They are able to achieve these time/effort savings because of their modular architecture approach with VIP solutions. For example, they are able to generate an emulation model very quickly because the simulation model is reusable as the software layer within the emulation model.

Customization

Generally speaking, there is always some customization that is required of off-the-shelf IP. For this reason, most IP suppliers provide a user guide to provide insights to their customers on how to customize the IP. Usually, this customization process is not an easy one and could take lot of time away from the engineers.

With SmartDV, customers state the changes they want at a high level. This is mapped into the SmartDV’s proprietary high-level language for the SmartCompiler, which then generates the customized IP. Their compiler technology has matured to such a level over the last decade that multiple versions of any design can be easily generated by just tweaking the parameters that are input to the compilers. This makes it easy for customization to get the IP as exactly required. Click here for a press release that talks about a competitive benchmark example.

Customer Benefits

SmartDV Support

Technical support is provided by core development engineers rather than separate field applications engineers. Yes, Bipul’s title is director of applications engineering but the actual team he manages for providing customer support is made up of development engineers. And the support team is available 24×7. This is a huge benefit as it cuts down the time required to address the support needs.

Homogeneity Across Various IP Solutions

Because SmartDV’s IP solutions are generated by smart compilers, they all use the same architecture. Because of this homogeneity, once a customer has used one SmartDV IP, it is very easy to use other SmartDV IPs. As a result, customers can save lot of time on successive projects.

Complete Test Suites

SmartDV VIP solutions come with a complete test suite. Customers get the regression suite along with the scripts to run it. Not all IP houses provide this. And some charge for it. SmartDV includes this as a part of the IP products they deliver.

Summary

This interview with Bipul has provided lots of insights into how and why SmartDV has taken the market leadership position in the VIP space and why they are quickly gaining ground in the Design IP space. Understanding these aspects would come in handy when choosing one’s design and verification IP solutions for future chip projects. You can check SmartDV’s extensive IP solutions offerings at their Products Page. Their sweet spot IP solutions address MIPI, Video, Storage and Networking applications including RISC-V and ARM-based Networking SoCs.

Also Read:

SmartDV Expands Its Design IP Portfolio with an Acquisition

CEO Interview: Deepak Kumar Tala of SmartDV

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.