9 Trends of IoT in 2023by Ahmed Banafa on 01-03-2023 at 6:00 amCategories: IoT

The year 2023 will hit all 4 components of IoT Model:

- Sensors,

- Networks (Communications),

- Analytics (Cloud)

- Applications

With different degrees of impact.

IoT Trend 1: Growth in Data and Devices with More Human-Device Interaction

By the end of 2019 there were around 3.6 billion devices that are actively connected to the Internet… Read More

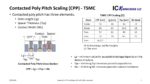

TSMC presented two papers on 3nm at the 2022 IEDM; “Critical Process features Enabling Aggressive Contacted Gate Pitch Scaling for 3nm CMOS Technology and Beyond” and “A 3nm CMOS FinFlexTM Platform Technology with Enhanced Power Efficiency and Performance for Mobile SOC and High Performance Computing Applications”.

When … Read More

Dan is joined by his podcast partner and producer Mike Gianfagna. Dan and Mike review the hot topics that trended on SemiWiki over the past year.

Included are discussions about how the semiconductor industry is changing, touching on Moore’s law, chiplets. and government intervention.The forces that are changing semis are… Read More

Sensors are inherently analog in nature, and they get digitized for processing by using an Analog to Digital Converter (ADC) block. At the recent IP SoC event I had the chance to see the presentation by Ken Potts, COO of Alphacore on their semiconductor IP for ADCs. I learned that Alphacore started out in 2012, now offering both standard… Read More

This. AI in PCB design is not a new idea. Other PCB software companies also make that claim. But when a mainstream systems technology company like Siemens talks about the subject, that is noteworthy. They already have an adaptive user interface (UI) for their mechanical modeling suite and to assist in low-code development for application… Read More

From the multi-chip-modules (MCM) of yester years to today’s System-in-Package (SiP) implementations, things have progressed a lot in terms of package technology. The chiplet movement is not only a big beneficiary of today’s advanced package technologies but drives further advances in this technology area. While a chiplets-based… Read More

-Micron off the proverbial cliff and falling faster

-Looking at a much longer/deeper decline in memory

-Layoffs, capex cuts, slowdowns- battening down the hatches

-Micron seems to imply more of a “U” or “L” shaped downcycle

Micron’s numbers as bad as we expected And much worse than most on the

…

Read More

Dan is joined by Dr. Thomas Mader, Tom is the Chief Operating Officer of OpenLight, a newly formed independent company by investments from Synopsys and Juniper Networks. Dr. Mader’s experience spans 27 years across the photonics and consumer electronics industries. Prior to the formation of OpenLight, he led the same team within… Read More

It’s been a bit more than a year since I interviewed Dr. Ashish Darbari, founder and CEO of Axiomise. I’ve been keeping an eye on Ashish and his colleagues, and I was surprised to learn that they recently celebrated their fifth anniversary as a company. I thought that this would be a good time to catch up with him to find out what’s happened… Read More

You don’t often hear about the inner workings of EDA tools and flows – the marketing guys much prefer telling us about all the exciting things their tools can do rather than the internal plumbing. But this matters for making design flows – and building these has largely been left to the users to sort out. That’s an increasing challenge… Read More

The Foundry Model Is Morphing — Again