I’ve noticed hybrid solutions popping up recently (I’m reminded of NXP’s crossover MCU released in 2017). These are generally a fairly clear indicator that market needs are shifting; what once could be solved with an application processor or controller or DSP or whatever, now needs two (or more) of these. In performance/power/price-sensitive applications, like many applications in the IoT, market pressure often demands just one processor.

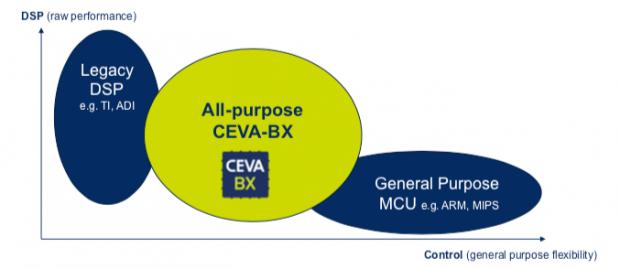

One way to cover this middle ground is to add functions to an existing architecture. So for example ARM provides hardware support for MAC (multiply-accumulate) operations, which you can use for example to build neural-net implementations on M-class subsystems. But it shouldn’t be a surprise that while an MCU with DSP extensions continues to be a good MCU and may compete on cost where DSP operation is undemanding, it is unlikely to be competitive in DSP-intensive applications. Conversely, a DSP amped-up to better perform controller functions is likely to suffer similar drawbacks in controller-intensive applications. In both cases, solutions can extend into the middle ground while not being ideal for the performance, power or value you would like to have.

Is this an artificial need in search of a problem? Not at all. The IoT has created a paradoxical requirement for very high levels of functionality (object and voice recognition for example) with responsive, even safety-critical performance and low power, while also being quite price-sensitive. Neural net workloads, modems, motor control and electrification in cars, bikes and scooters all need both DSP and control support with varying levels of demand between these two. You could require a DSP and a controller in every such application, a power and cost problem in many cases, or you could architect a true middle-ground solution. Which is what CEVA have done with their CEVA-BX product family, announced this week at CES.

Moshe Sheier (VP Marketing at CEVA) tells me that CEVA-BX is a new architecture, not an extension to an existing architecture, designed for the high-complexity signal handling performance and low power expected of DSP kernels, together with the high-level programming and compact code sizes expected for the established control code base. It supports parallel scalar compute engines and clocks at 2 GHz in TSMC 7nm, offering 4X the horsepower of the current CEVA-X2 DSP. The Instruction Set Architecture (ISA) supports Single Instruction Multiple Data (SIMD) widely used in neural network inference, noise reduction and echo cancellation, as well as native complex math and a range of floating-point options, in support of applications like high accuracy sensor fusion and GNSS positioning algorithms.

To meet control performance expectations, the CEVA-BX architecture incorporates features including a large orthogonal general-purpose register set for compiler efficiency, new Branch Target Buffer (BTB) for minimizing branch overhead, a hardware loop buffer for reduced power consumption of code loops, a fully cached memory subsystem, and native support for all standard C types. The CoreMark/MHz score of 4.5 places it comfortably in the MCU pack. CEVA-Xtend is available to add proprietary ISA instructions to the architecture to accelerate proprietary algorithms and to leverage CEVA’s automatic Queue and Buffer management mechanisms when integrating co-processors (for example in 5G PHY control) or creating a cluster of CEVA-BX cores.

CEVA-BX comes with extensive software libraries, both fundamental (DSP neural net, neural net frameworks, compiler, debugger and RTOS) and application (cellular IoT and GNSS ISA extensions, CEVA ClearVox noise reduction for voice-activated systems and CEVA voice recognition). Quite a starting package for application developers.

The family currently contains two members: CEVA-BX1 and CEVA-BX2 which differ in range of MACs offered. CEVA-BX2 comes with quad 32×32-bit MACs and octal 16×16-bit MACs and is intended to address very intensive DSP workloads like 5G PHY control, beam-forming and neural net workloads at up to 16 GMACs/second. CEVA-BX1 is more for the value to mid-range applications in narrow-band IoT communication and always-on (ie low power) voice-pickup or sensor fusion at up to 8 GMACs/second. These cores are currently available to CEVA lead customers and will become available for general use at the end of Q1 2019

Back to the market question. IoT devices are becoming a lot smarter than the dumb nodes we originally expected, not just in being able to do local processing but also in adding local intelligence so that communication with the cloud can be minimized and temporary loss of communication can be tolerated. That demands higher DSP workloads in communication, in neural nets, in motor control and other functions for which the traditional DSP+controller architecture is apparently struggling to keep up. The hybrid architecture approach is worth a look, especially since there is a lot of detail I skipped in this brief review. CEVA is presenting at CES this week so see them there if you can, otherwise check the product details HERE.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.