In the dynamic landscape of chip design, two trends stand out as game-changers: the rise of the RISC-V instruction set architecture (ISA) and the advent of Software Defined products. Today, we delve into why these trends are not just shaping the industry but propelling companies like Andes and Menta to the forefront of innovation.… Read More

Tag: isa

Is your career at RISK without RISC-V?

I am delighted to share my technical insights into RISC-V in this article to inspire and prepare the next generation of chip designers for the future of the open era of computing. If you understand how we build complex electronic devices like desktops and smartphones using processors, you would be more interested in learning and… Read More

SiFive’s Approach to Embedding Intelligence Everywhere

Before the advent of RISC-V, designers looking for embedded processors were effectively limited to a handful of proprietary processors using ISAs from decades ago. While the major ISAs are being updated and enhanced, they also are facing limitations from many decisions made over many years. RISC-V was conceived with a clean… Read More

Learn About Implementing SmartNICs, an Achronix White Paper

We have all seen the announcements to provide ever-increasing network capabilities within the data centers. Enabling these advances are improvements in connectivity including SerDes, PAM4, optical solutions, and many others. It seems 40G is old news now, and the current push is for 400G – things are changing very quickly.… Read More

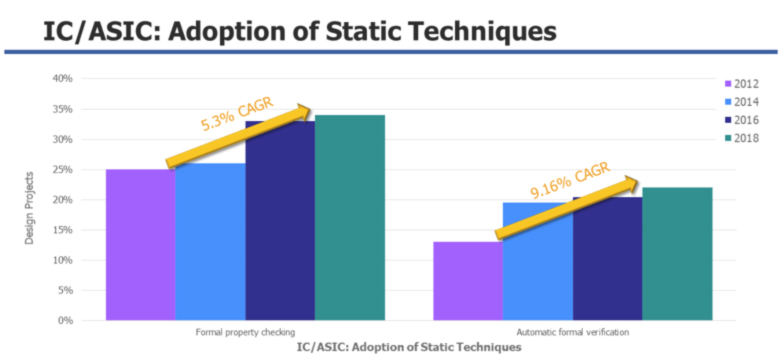

IC Integrity Thesis

Most of my investments are associated with large changes in the semiconductor industry. These changes create opportunities for new and disruptive technologies. I also look to find solutions that provide a compelling reason to adopt a new technology or approach. When talking about a new approach, it often takes longer to overcome… Read More

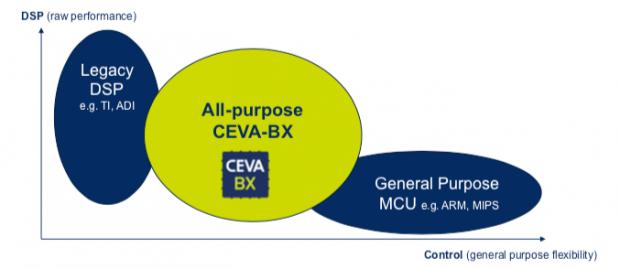

CEVA-BX: A Hybrid DSP and Controller

I’ve noticed hybrid solutions popping up recently (I’m reminded of NXP’s crossover MCU released in 2017). These are generally a fairly clear indicator that market needs are shifting; what once could be solved with an application processor or controller or DSP or whatever, now needs two (or more) of these. In performance/power/price-sensitive… Read More

Imperas and RISC-V

I met Imperas at TechCon this year because I wanted to become a bit more knowledgeable about virtual modeling. That led me to become more interested in RISC-V and a talk given by Krste Asanovic of UCB and SiFive. My takeaway surprised me. I had thought this was an open-source David versus proprietary Goliaths (Intel and ARM) battle… Read More

Security and RISC-V

One of the challenges in the RISC-V bid for world domination may be security. That may seem like a silly statement, given that security weaknesses are invariably a function of implementation and RISC-V doesn’t define implementation, only the instruction-set architecture (ISA). But bear with me. RISC-V success depends heavily… Read More

The Dawn of a New RISC

The 8[SUP]th[/SUP] RISC-V Workshop was held in Barcelona May 7-10 with 325 attendees from 150+ companies and was the biggest RISC-V event outside of Silicon Valley, demonstrating the momentum of the RISC-V Foundation and the growth of the ecosystem in Europe.… Read More

RISC-V Business

I was at the 7[SUP]th[/SUP] RISC-V Workshop for two days this week. It was hosted by Western Digital at their headquarters in Milpitas. If you have not been following RISC-V, it is an open source Instruction Set Architecture (ISA) for processor design. The initiative started at Berkeley, and has been catching on like wildfire. … Read More