I love it when EDA companies send their engineers to DAC because I learn more of the unvarnished truth about their products. I met with Bill Thomas of Aldec to get an update on their HW prototyping boards, then two NEC engineers to learn about High Level Synthesis.

HW Prototyping

Bill Thomas, Research Engineer at Aldec

Q: What are you showing at DAC this year?

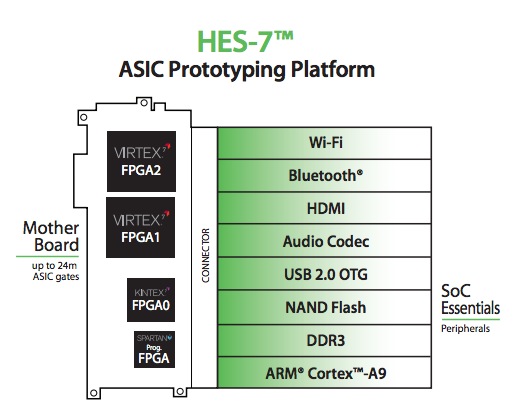

We’re showing the HES-7 boards, with up to 96 million gates for ASIC prototyping. You can also daisy chain two backplances together. We reuse boards for prototyping and emulation acceleration, one board for both uses. (other companies have two separate product lines)

Q: How is HES-7 unique?

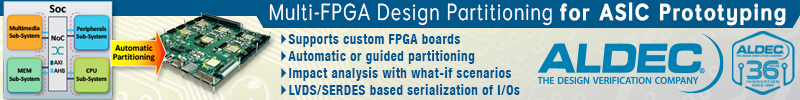

With the HES DVM (Design Verification Manager) software you can do auto-partitioning , saving you time. There are standard PCIE connectors to a host PC, then connect it to any simulator like Riviera PRO, ModelSim, Synopsys VCS, Cadence Incisive, etc.

Debugging in the hw emulation, both static and dynamic probes. View waveforms on your favorite viewer. SoC Emulation platform enables both software engineer to see the memory and do CPU debugging, easy to add any JTAG CPU debugger. SW guys want to see memory for debugging.

SCE-MI Infrastcture – allows you to connect a TLM testbench to your emulator. It’s an Acellera standard. Synthesizer Transactor – more efficient way to accelerate the emulator, low overhead.

Both HW and SW developers benefit from the same SoC Emulation.

High Level Synthesis

M. Hamabe, K. Wakabayashi, Ph. D. from NEC

I remember first hearing about the NEC tool called CyberWorkBench when working at Yxi, another C-based High Level Synthesis (HLS) company several years ago.

Q: What is unique about CyberWorkBench?

Advantages – ie 8 lines of C code versus 100 lines of RTL code, easier to get to timing disclosure. Based on constraints can quickly create many different architectures.

Q: What is the history of the HLS tools?

– Tool started in the 1980’s. Most Japanese companies are using CWB. 1993 first SONET controller chip designed in CWB.

– Originally an in-house tool only at NEC, but now open to the market place.

Q: Who is using it?

– Customers: NEC, Renesas, Panasonic, Toyota, JAXA, Toshiba, Hitachi, Advantest, JVC, Fujitsu.

Q: How do you compare with Forteand Catapult?

– They do mostly DSP applications, while NEC works well for control-centric designs.

Bluespec – OK for controller, but no scheduling capabilities, not so HLS.

Q: What is the input language?

Input: Both SystemC and C.

Behavioral synthesis, low power synthesis, GUI for best QOR.

Input – both timed and untimed C code using the “$” pragma.

Automatic communications protocol I’F synthesis – support auto and manual scheduling modes.

Q: What is the output?

The output is cycle-accurate models. RTL simulation is too slow, so C based models with cycle accuracy simulate fast and accurate. Timing debugging in ANSI C.

Also supports static verification with formal tools.

Inputs – Verilog/VHDL are auto-converted into SystemC.

All-In-C : HLS for controller, DSP, etc. Both are equally synthesized. (Forte, Catapult are more DSP centric).

Output to both ASIC and FPGA versions

Q: How do you use your HLS tool?

Explore the architectural output space using a GUI, almost a push-button approach suitable for SW designers without having much HW experience.

Q: Why is writing C code preferred to RTL code?

C versus RTL code: from 7X to 10X less lines of code in C. Simulation speeds in C are 203X faster.

From a single C input you can create many RTL outputs to meet the speed, latency and area desired.

Q: How are sales?

First US customer last year, we are number one in Japan, time to grow here in USA.

Q: What is the relationship with Aldec?

We have a good partnership with Aldec to span a broader spectrum of EDA tools and emulation.

lang: en_US

Share this post via:

Comments

0 Replies to “HW Prototyping and HLS at DAC”

You must register or log in to view/post comments.