You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Verification is a resource limited ‘quest’ to find as many bugs as possible before shipping. It’s a long, difficult, costly search, constrained by cost, time and quality. For a multi-billion gate ASIC,

The search space is akin to a space search; practically infinite

In this article we talk about the quest for bugs at the system-level,… Read More

You’re building an IP, subsystem or SoC and you want to use a prototype together with a software testbench to drive extensive validation testing. I’m not talking here about the software running on the IP/SoC processor(s); the testbench should wrap around the whole DUT. This is a very common requirement. The standard approach to… Read More

Unless you’ve been in hibernation for a while, you probably know that a lot more chip design is happening in system companies these days. This isn’t just for science experiments; many of these designs are already being used in high-value applications. This development is captive – systems companies generally don’t want… Read More

I love it when EDA companies send their engineers to DAC because I learn more of the unvarnished truth about their products. I met with Bill Thomas of Aldec to get an update on their HW prototyping boards, then two NEC engineers to learn about High Level Synthesis.

HW Prototyping

Bill Thomas, Research Engineer at Aldec

… Read More

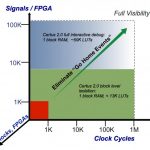

ASIC prototyping in FPGAs is starting to trend on SemiWiki. As FPGA technology becomes more advanced customers tell me that the traditional debug tools are inadequate. Faced with the very restrictive debugging capabilities and very long synthesis/place/route times the debugging cycle in these prototype platforms are quite… Read More

Last month the folks at Tektronix did something very useful, they invited 30 engineers to talk directly with their chief engineer of embedded instrumentation as part of “Meet the Experts” in Santa Clara, CA.

Brad Quinton, Chief Architect created a new and efficient approach of embedding instrumentation in your … Read More

One technology that has quietly gone mainstream in semiconductor design is FPGA prototyping. That is, using an FPGA version of the design to run extensive verification. There are two approaches to doing this. The first way is simply to build an prototype board, buy some FPGAs from Xilinx or Altera and do everything yourself. The… Read More