You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 24

[name] => TSMC

[slug] => tsmc

[term_group] => 0

[term_taxonomy_id] => 24

[taxonomy] => category

[description] =>

[parent] => 158

[count] => 624

[filter] => raw

[cat_ID] => 24

[category_count] => 624

[category_description] =>

[cat_name] => TSMC

[category_nicename] => tsmc

[category_parent] => 158

[is_post] =>

)

WP_Term Object

(

[term_id] => 24

[name] => TSMC

[slug] => tsmc

[term_group] => 0

[term_taxonomy_id] => 24

[taxonomy] => category

[description] =>

[parent] => 158

[count] => 624

[filter] => raw

[cat_ID] => 24

[category_count] => 624

[category_description] =>

[cat_name] => TSMC

[category_nicename] => tsmc

[category_parent] => 158

[is_post] =>

)

All-Digital In-Memory Computingby Tom Dillinger on 03-15-2021 at 6:00 amCategories: Events, Foundries, TSMC

Research pursuing in-memory computing architectures is extremely active. At the recent International Solid State Circuits conference (ISSCC 2021), multiple technical sessions were dedicated to novel memory array technologies to support the computational demand of machine learning algorithms.

The inefficiencies associated… Read More

Register File Design at the 5nm Nodeby Tom Dillinger on 03-10-2021 at 2:00 pmCategories: Events, Foundries, TSMC

“What are the tradeoffs when designing a register file?” Engineering graduates pursuing a career in microelectronics might expect to be asked this question during a job interview. (I was.)

On the surface, one might reply, “Well, a register file is just like any other memory array – address inputs, data inputs and outputs, read/write… Read More

There are reports in the media that TSMC is now planning six Fabs in Arizona (the image above is Fab 18 in Taiwan). The original post I saw referred to a Megafab and claimed six fabs with 100,000 wafers per month of capacity (wpm) for $35 billion dollars. The report further claimed it would be larger than TSMC fabs in Taiwan.

This report… Read More

– Semiconductor shortage is like toilet paper shortage in early Covid

– Panic buying, hoarding, double ordering will cause spike

– Could cause a year+ of dislocation in chip makers before ending

– Investors, Govt & Mgmt will get a wake up call from earnings hit

Auto industry is just a prominent tip … Read More

– Semi Situation Stems from long term systemic neglect

– Will require much more than money & time than thought

– Fundamental change is needed to offset the financial bias

– Auto industry is just the hint of a much larger problem

Like recognizing global warming when the water is up to your neck

The problem… Read More

Resistive RAM (ReRAM) technology has emerged as an attractive alternative to embedded flash memory storage at advanced nodes. Indeed, multiple foundries are offering ReRAM IP arrays at 40nm nodes, and below.

ReRAM has very attractive characteristics, with one significant limitation:

- nonvolatile

- long retention time

- extremely

…

Read More

Now that semiconductor conferences are virtual there are better speakers since they can prerecord and we have the extra time to do a better job of coverage. Even when conferences go live again I think they will also be virtual (hybrid) so our in depth coverage will continue.

ISSCC is one of the conferences we covered live since it’s… Read More

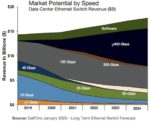

We have seen that the interface IP category is seeing incredibly high growth rate over the last two decades and we expect this category to generate an ongoing high source of IP revenues for at least another decade. But if we dig into the various successful protocols like PCI Express, Ethernet or USB, we can detect a common function … Read More

-KLAC- Solid QTR & Guide but flat 2021 outlook

-Display down & more memory mix

-KLAC has very solid Dec Qtr & guide but 2021 looks flattish

-Mix shift to memory doesn’t help- Display weakness

-Despite flat still looking at double digit growth

-EUV driven business may see some slowing from digestion

As always, … Read More

It is quite amazing that silicon-based devices have been the foundation of our industry for over 60 years, as it was clear that the initial germanium-based devices would be difficult to integrate at a larger scale. (GaAs devices have also developed a unique microelectronics market segment.) More recently, it is also rather … Read More