It’s always a pleasure when a vendor gives a really informative, vendor-independent presentation on what’s happening in some domain of the industry and wraps up with (by that point) a well-deserved summary of that vendor’ solutions in that space. Ron Lowman did just that at the Linley conference on Mobile and Wearables, where … Read More

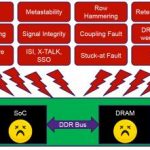

Why using new DDR4 allow designing incredibly more efficient Server/Storage applications?

The old one-size-fits-all approach doesn’t work anymore for DDR4 memory controller IP, especially when addressing the enterprise segments, or application like servers, storage and networking. For mobile or high end consumer segments, we can easily identify two key factors: price (memory amount or controller footprint) … Read More

10nm Will Be an Epic Process Node!

In the history of the fabless semiconductor industry the foundries have always been a process node or two behind the leading semiconductor manufacturers. Starting in Q1 2017, for the first time in fabless semiconductor history, the foundries will have a process node advantage. This is horrible news for some but great news for … Read More

Webinar alert – Hybrid prototyping for ARMv8

All the talk about ARM server SoCs has been focused on who will come up with the breakthrough chip design. Watching trends like OPNFV develop suggests the big breakthrough is more likely to come on the ARMv8 software side. How do you quickly validate ARMv8 software when you don’t have the exact ARMv8 SoC target?… Read More

Learn How to Debug UVM Test Benches Faster – Upcoming Synopsys Webinar

UVM for developing testbenches is a wonderful thing, as most verification engineers will attest. It provides abstraction capabilities, it encapsulates powerful operations, it simplifies and unifies constrained-random testing – it has really revolutionized the way we verify at the block and subsystem level.

However great… Read More

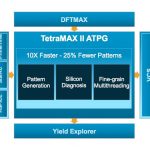

EDA Tool for ATPG – Refactor or Rewrite?

In the life of all EDA software tools comes that moment when new requirements make developers stop and ask, should I continue to refactor the existing code or just start all over from scratch using a new approach? Synopsys came to that junction point when ATPG run times were reaching days or even weeks on the largest IC designs, something… Read More

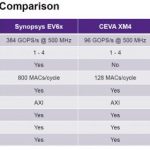

Synopsys Launch EV6x Vision Processor… Challenging the Competition!

When Synopsys bought Virage Logic in 2010, ARC processor IP was in the basket, but at that time ARC processor core was not the most powerful on the market, and by far. The launch of EV6x vision processor sounds like Synopsys has moved ARC processor core by several orders of magnitude in term of processing power. EV6x deliver up to 100X… Read More

HBM controller IP holds the key to bandwidth

We were waiting to see what a different roster including SK Hynix and Synopsys would have to say on HBM in the latest Open Silicon webinar. This event focused on HBM bandwidth issues; a packaging session on 2.5D interposers was promised for a future webinar.… Read More

Circuit Simulation Panel Discussion at #53DAC

Four panelists from big-name semiconductor design companies spoke about their circuit simulation experiences at #53DAC in Austin this year, so I attended to learn more about SPICE and Fast SPICE circuit simulation. I heard from the following four companies:… Read More

TMR approaches should vary by FPGA type

We’ve introduced the concepts behind triple modular redundancy (TMR) before, using built-in capability in Synopsys Synplify Premier to synthesize TMR circuitry into FPGAs automatically. A recent white paper authored by Angela Sutton revisits the subject… Read More