As embedded systems continue to become more complex and integrate greater functionality, SoC developers are faced with the challenge of developing more powerful, yet more energy-efficient devices. The processors used in these embedded applications must be efficient to deliver high levels of performance within limited power… Read More

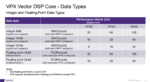

DSP IP for High Performance Sensor Fusion on an Embedded Budget

Whether we realize it or not, everyday applications we use depend on data gathered by sensors. We can bet that pretty much every application uses at least a couple of different types of sensors, if not more. That is because different types of sensors are better suited to collect data depending on the application, the environment … Read More

Memory Security Relies on Ultra High-Performance AES-XTS Encryption/Decryption

A recent SemiWiki post covered the topic of protecting high-speed interfaces in data centers using security IP. That post was based on a presentation made by Dana Neustadter at IP-Soc Silicon Valley 2022 conference. Dana’s talk was an overview of various interfaces and Synopsys’ security IP for protecting those interfaces. … Read More

Casting Light on OpenLight’s Open Silicon Photonics Platform

For many decades now, modern optical technology has been deployed in networking infrastructure, for long haul and medium haul links to support internet communications. The foundation of this technology is photonics, which is the science of generation, manipulation and detection of light for performing functions otherwise… Read More

Very Short Reach (VSR) Connectivity for Optical Modules

Bandwidth, latency, power and reach are always the key points of focus when it comes to connectivity. As the demand for more data and higher bandwidth connectivity continue, power management is gaining a lot of attention. There is renewed interest in pursuing silicon photonics to address many of these challenges. There are many… Read More

Protecting High-Speed Interfaces in Data Centers with Security IP

The never ending appetite for higher bandwidths, faster data interfaces and lower latencies are bringing about changes in how data is processed at data centers. The expansion of cloud to the network edge has introduced broad use of artificial intelligence (AI) techniques for extracting meaning from data. Cloud supercomputing… Read More

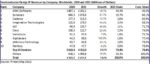

Design IP Sales Grew 19.4% in 2021, confirm 2016-2021 CAGR of 9.8%

Design IP Sales reached $5.45B in 2021, or 19.4% YoY after 16% in 2020, on-sync with semiconductor growth of 26.2% in 2021 according to WSTS. IPnest has released the “Design IP Report” in May 2022, ranking IP vendors by category (CPU, DSP, GPU & ISP, Wired Interface, SRAM Memory Compiler, Flash Memory Compiler, Library and I/O,… Read More

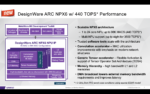

Bigger, Faster and Better AI: Synopsys NPUs

AI-based applications are fast advancing with evolving neural network (NN) models, pushing aggressive performance envelopes. Just a few years ago, performance requirements of NN driven applications were at 1 TOPS and less. Current and future applications in the areas of augmented reality (AR), surveillance, high-end smartphones,… Read More

Synopsys Tutorial on Dependable System Design

Synopsys hosted a tutorial on the last day of DVCon USA 2022 on design/system dependability. Which here they interpret as security, functional safety, and reliability analysis. The tutorial included talks from DARPA, AMD, Arm Research and Synopsys. DARPA and AMD talked about general directions and needs, Arm talked about their… Read More

Use Existing High Speed Interfaces for Silicon Test

The growth of complexity for silicon test as it relates to test data volume and test times is driven by multiple concurrent factors. One dimension is simply the increase in silicon complexity. However, other factors are playing a role as well. These include higher reliability requirements for new applications such as automotive,… Read More