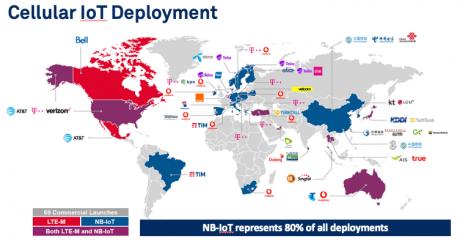

Cellular as a method to communicate with the IoT is on a tear for obvious reasons. It’s long-range with no concerns about the lesser reach of Bluetooth or Wi-Fi, it needs no added infrastructure since it already works with 2G/3G/4G (and ultimately 5G I presume) and it’s designed for ultra-low power, supporting those devices expecting… Read More

Semiconductor Intellectual Property

ARM, NXP Share Usage, Challenges at Synopsys Lunch

Synopsys runs a “Industry verifies with Synopsys” lunch at each DVCon, which isn’t as cheesy as the title might suggest. The bulk of the lunch covers user presentations on their use of Synopsys tools which I find informative and quite open, sharing problems as much as successes. This year, Eamonn Quiqley, FPGA engineering manager… Read More

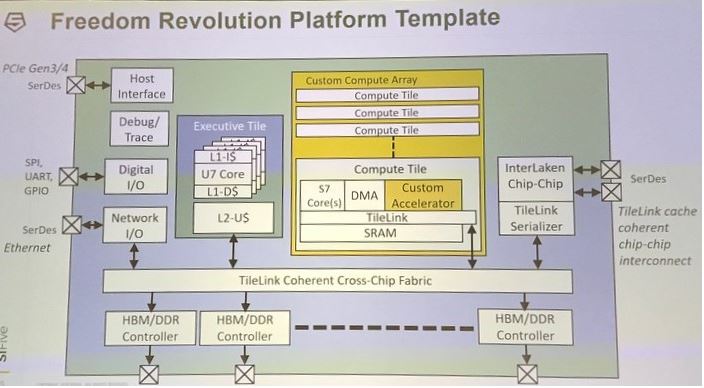

The Revolution Evolution Continues – SiFive RISC-V Technology Symposium – Part II

During the afternoon session of the Symposium, Jack Kang, SiFive VP sales then addressed the RISC-V Core IP for vertical markets from consumer/smart home/wearables to storage/networking/5G to ML/edge. Embedding intelligence from the edge to the cloud can occur with U Cores 64-bit Application Processors, S Cores 64-bit Embedded… Read More

Qualcomm Intel Facebook and Semiconductor IP

What does Qualcomm, Intel, and Facebook have in common? Well, for one thing they all bought network onchip communications (NoC) IP companies. As I have mentioned before, semiconductor IP is the foundation of the fabless semiconductor ecosystem and I believe this trend of acquisitions will continue. So, if you are going to start… Read More

The Revolution Evolution Continues – SiFive RISC-V Technology Symposium – Part I

SiFive held a RISC-V Technology Symposium on February 26 at the Computer History Museum in Mountain View. Keith Witek, SiFive SVP Corporate Development and Strategy kicked off the event and introduced the first keynote speaker Martin Fink, Western Digital CTO, at the time acting CEO of the RISC-V Foundation (as of this writing,… Read More

Segmenting the Machine-Learning Hardware Market

One of the great pleasures in what I do is to work with people who are working with people in some of the hottest design areas today. A second-level indirect to be sure but that gives me the luxury of taking a broad view. A recent discussion I had with Kurt Shuler (VP Marketing at Arteris IP) is in this class. As a conscientious marketing… Read More

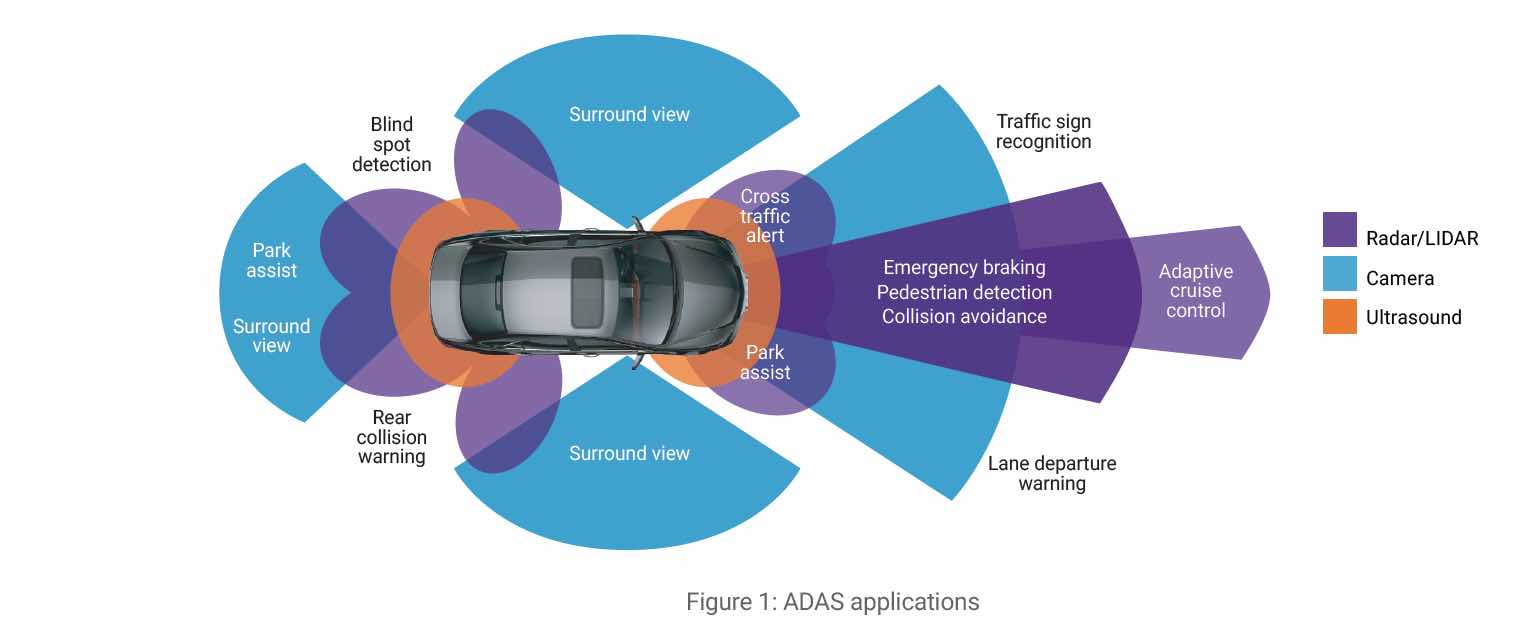

Accelerating SOC Development for Automobile Applications

No area of electronics is moving faster than automotive semiconductors. Everyone has been talking about the increasing electronics content of automobiles for decades. With Advanced Driver Assistance System (ADAS) and autonomous driving becoming a reality the pace has picked up even more. These new designs combine just about… Read More

eSilicon Bucking the Trend at OFC with 7nm SerDes

A recent press release from eSilicon caught my eye. The company has been touting their 7nm SerDes quite a bit lately – reach, power, flexibility, things like that. While those capabilities are important, any high-performance chip needs to work in the context of the system, which usually contains technology from multiple sources.… Read More

Arm Deliver Their Next Step in Infrastructure

Arm announced their Neoverse plans not long ago at TechCon 2018. Neoverse is a brand, launched by Arm, to provide the foundations for cloud to edge infrastructure in support of their vision of a trillion edge devices. To a cynic this might sound like marketing hype. Sure, they’re widely used in communications infrastructure and… Read More

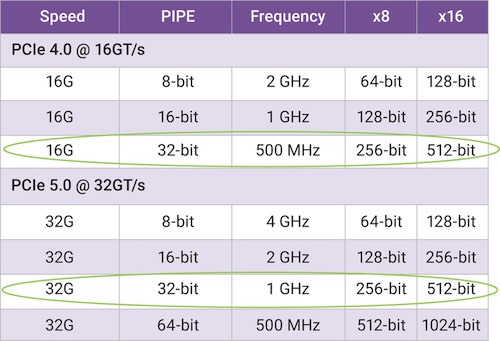

PCIe 5.0 Jumps to the Fore in 2019

2019 will be a big year for PCIe. With the approval of version 0.9 of the Base Layer for PCIe 5.0, implementers have a solid foundation to begin working on designs. PCIe 4.0 was introduced in 2017, before that the previous PCIe 3.0 was introduced in 2010 – ages ago in this industry. In fact, 5.0 is so close on the heels of 4.0, many products… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era