I have observed before that the success of an AI engine at the edge rests heavily on the software interface to drive that technology. Networks trained in the cloud need considerable massaging to optimize for smaller and more specialized edge devices. Moreover, an AI task at the edge depends on a standalone pipeline demanding a mix… Read More

Semiconductor Intellectual Property

Emerging Stronger from the Downturn

It was refreshing to hear a talk focused on emerging stronger from the downturn when the news and media are focused on the gloom. At the recent Siemens EDA User2User conference, Joe Sawicki, executive vice president, IC, gave an uplifting keynote talk to the audience. He highlighted a secular growth trend happening in the semiconductor… Read More

Silicon Catalyst and Arm announce $150,000 Silicon Startup Contest!

As I sift through mounds of semiconductor press releases trying to figure out the relevance (with mixed results) I consider it a learning experience even when they don’t really tell me anything. This one however tells me two very important things:

1) Arm is a much more competitive company with the new leadership. I saw a noticeable… Read More

Is Your Interconnect Strategy Scalable?

“Strategy” is a word sometimes used loosely to lend an aura of visionary thinking, but in this context, it has a very concrete meaning. Without a strategy, you may be stuck with decisions you made on a first-generation design when implementing follow-on designs. Or face major rework to correct for issues you hadn’t foreseen. Making… Read More

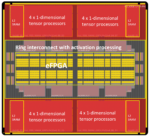

Reconfigurable DSP and AI IP arrives in next-gen InferX

DSP and AI are generally considered separate disciplines with different application solutions. In their early stages (before programmable processors), DSP implementations were discrete, built around a digital multiplier-accumulator (MAC). AI inference implementations also build on a MAC as their primitive. If the interconnect… Read More

Memory Solutions for Modem, EdgeAI, Smart IoT and Wearables Applications

Memories have always played a critical role, both in pushing the envelope on the semiconductor process development front and supporting the varied requirements of different applications and use-cases. The list of the various types of memories in use today runs long. At a gross level, we can classify memories into volatile or … Read More

Alphawave Semi Showcases 3nm Connectivity Solutions and Chiplet-Enabled Platforms for High Performance Data Center Applications

There were quite a few announcements at the TSMC Technical Symposium last week but the most important, in my opinion, were based on TSMC N3 tape-outs. Not only is N3 the leading 3nm process it is the only one in mass production which is why all of the top tier semiconductor companies are using it. TSMC N3 will be the most successful node… Read More

Formal-based RISC-V processor verification gets deeper than simulation

The flexibility of RISC-V processor IP allows much freedom to meet specific requirements – but it also opens the potential for many bugs created during the design process. Advanced processor features are especially prone to errors, increasing the difficulty and time needed for thorough verification. Born out of necessity, … Read More

Podcast EP158: The Benefits of a Unified HW/SW Architecture for AI with Quadric’s Nigel Drego

Dan is joined by Nigel Drego, the CTO and Co-founder at Quadric. Nigel brings extensive experience in software and hardware design to his role at Quadric. Nigel is an expert in computer architectures, compiler technology, and software frameworks.

Dan explores the unique and unified HW/SW architecture developed by Quadric with… Read More

CEO Interview: Ravi Thummarukudy of Mobiveil

Mobiveil Marks 11th Anniversary

Ravi Thummarukudy is Mobiveil’s Chief Executive Officer and a founder. He and I recently spent an enjoyable afternoon getting acquainted as I learned more about Mobiveil. It’s an inspiring story of a technology company in the semiconductor space helping customers and prospering.

Eleven-year-old… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!