A week ago I was reading an article written by Daniel Nenni where he emphasised about semiconductor acquisitions to fuel innovation. We would see that in a larger space, not only in semiconductor and FPGA manufacturing companies (e.g. Intel and Altera) but also in the whole semiconductor ecosystem. If we see it from technical perspective,… Read More

Synopsys to Acquire Atrenta

I was at the DAC kickoff this evening in the Intercontinental Hotel. I was talking to Dave DeMaria, the senior marketing guy at Synopsys and he told me of a couple of minor press releases due to hit the wire tomorrow morning, didn’t sound important enough to be blogworthy. Aart was there too although I didn’t speak to him.… Read More

Vacationing with the Fabless Semiconductor Ecosystem!

The Design Automation Conference is the largest and most diverse event in the fabless semiconductor ecosystem. Next week in San Francisco you will see technology and people you have never seen before. You will benefit from the efforts of hundreds of thousands of semiconductor professionals like myself who have dedicated their… Read More

Synopsys Software Integrity: Find All the Bugs

A couple of days ago Synopsys announced that they were acquiring Quotium’s product Seeker. This is an interactive application security testing (IAST) product. Synopsys are acquiring the product and the R&D team, not the whole of Quotium. The Seeker solution is a pioneering solution for IAST that helps businesses find high-risk… Read More

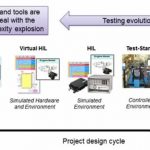

Virtual HIL and the 100M LOC car

Aerospace and defense applications have traditionally leveraged hardware-in-the-loop (HIL) testing to overcome several issues. A big one is how expensive the physical system is. Even breaking down the system into subsystems for test can still be too expensive when fielding more than a couple test stations. Modeling elements… Read More

Synopsys Earnings Call

Synopsys had their earnings announcement and call last week. They were good. In Aart’s own words:I’m happy to report that our second quarter results were very strong and solidify our outlook for the full year. We delivered revenue of $557 million, non-GAAP earnings per share of $0.68 and $155 million in operation cash flow.… Read More

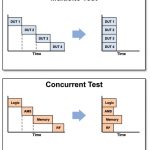

Saving Time and Money on Your Next SoC Project

Every SoC project that I know of wants to finish on time, under budget, and maximize profits per device. When I first started out doing DRAM design I learned that we could maximize profit by doing shrinks of existing designs, move from ceramic to plastic packages, and reduce the amount of time spent on a tester. Today, the economic … Read More

SoC’s Shift Left Needs Software Integrity

Since Aart de Geus, co-CEO and co-founder of Synopsys, gave his keynote at the Synopsys User Group (SNUG) conference in Silicon Valley last March, I’ve been hearing a lot more about the “Shift Left” in semiconductor design. Although I couldn’t attend Synopsys’ 25[SUP]th[/SUP]SNUG, I found some short videos on the Synopsys website… Read More

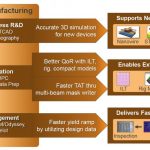

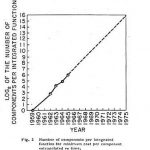

TCAD Enables Moore’s Law to Continue

We live in very interesting times, you can wear an Android watch from Samsung that uses 14 nm FinFET technology, attend the 52nd DAC conference in June to learn about EDA and IP vendors supporting FinFET, and read about research work for new devices down to 5 nm. TCAD is that critical software technology that enables the development… Read More

25 Years of SNUG; 50 Years of Moore’s Law

Earlier this week it was the Synopsys user group meeting SNUG. Not just any old SNUG but the 25th Annual SNUG. The first one was 15th March 1991 and was attended by 100 people. At the time, Synopsys had annual revenues of $22M. This year, the various SNUGs around the world will have a total attendance of 10,000 people and Synopsys revenue… Read More