You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 791

[filter] => raw

[cat_ID] => 14

[category_count] => 791

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 791

[filter] => raw

[cat_ID] => 14

[category_count] => 791

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

Andreas Kuehlmann is the general manager of what is officially now known as the Software Integrity Group of Synopsys, what you might think of as Coverity although they have made some acquisitions too, so they now have a broader technology base. I sat down to talk to him last week.

He was brought up in Germany and came to the US in 1991 … Read More

Antun Domic is the GM of the Design Group at Synopsys. I sat down with him a couple of weeks ago.

His name is Croatian although, of course, there was no Croatia back then it was part of Yugoslavia. But in fact he grew up in Chile and went to university there where he studied EE and math. He came to the US as a grad student and did a PhD at MIT in … Read More

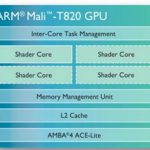

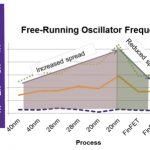

ARM is a well-known semiconductor IP provider and they often create a reference design so that SoC companies can have a starting point to work with. On the GPU side of IP the ARM engineers have an architecture called Mali, and a recent webinar hosted by Synopsys reviewed how the physical design area was minimized by using a combination… Read More

Actual users of circuit simulators told their design and simulation stories at DAC during a luncheon sponsored by Synopsys on June 8th. I always prefer to hear from a design engineer versus a marketing person about what tool they use for circuit simulation, and how it helps them analyze their design goals. This year there were engineers… Read More

One of the most interesting presentations that I went to was the last presentation at the Synopsys Custom Lunch (no, the lunch wasn’t custom, we all got the same, but the presentations were about custom design). Since the last presentation was by Synopsys themselves and not by a customer, it wouldn’t seem promising that it could … Read More

In an overwhelmingly digital world, there is a constant cry about the analog design process being slow, not automated, going at its own pace in the same old fashion, and so on. And, the analog world is not happy with the way it’s getting dragged into imperfect automation so it can be more like the digital world. True, the analog world… Read More

Last week I sat down and talked to Bijan Kiani of Synopsys. He has marketing responsibility for design implementation products at Synopsys spanning digital, custom and analog mixed signal (AMS).

He was born in Iran and after high school he moved to the UK. He got his PhD degree from University of Edinburgh. It turns out that I was doing… Read More

The CEO Fireside Chats were my very favorite part of #52DAC. Dr. Walden Rhines, Lip-Bu Tan, and Dr. Aart de Geus are heroes of the EDA industry, absolutely. I saw all three Fireside Chats and the one word that I’m left with is INSPIRED! … Read More

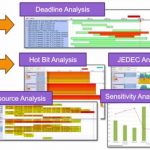

In optimizing SoC design for performance, there is so much focus on how fast a CPU core is, or a GPU core, or peripherals, or even the efficiency of the chip-level interconnect. Most designers also understand selecting high performance memory at a cost sweet spot, and optimizing physical layout to clock it as fast as possible within… Read More

Actually, like anyone who has been in EDA for more than a decade or two (or three) I know quite a bit about Aart. But I still learned quite a bit about his views at the Fireside Chat at DAC where Ed Sperling talked to Aart for three-quarters of an hour.

Aart has a great talent at taking various small trends in the industry and aggregating … Read More