You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4394

[filter] => raw

[cat_ID] => 157

[category_count] => 4394

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

Arasan recently adopted ClioSoft for data management (DM) for design and development of Arasan’s Silicon IP products. This morning I talked to Erik Peterson, Senior CAD and Verification Engineer AMS Design about their experiences bringing up ClioSoft.

Data management infrastructure is critical with engineering projects… Read More

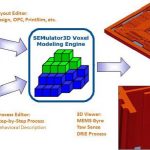

The design and manufacture of MEMS is very different and in many ways more complex process than even the most advanced ICs. MEMS involve multiple degrees of freedom (i.e. the device to exhibit different characteristics under different physical state, motion or mechanics), making fabrication of MEMS extremely complex; and hence… Read More

I was tempted to call this piece “if you’re not using an FPGA, you’re doing it wrong,” but that didn’t quite capture the whole picture. Social memes aside, the FPGA as we know it is undergoing a serious transformation into a full blown SoC, and 2014 is the year that will usher in one of the biggest changes in the history of embedded design.… Read More

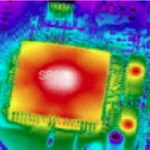

In the 1970’s we designed ICs first and when silicon came back then we measured the power and junction temperature. At that time there were no EDA simulation tools or models for full-chip power and temperature analysis. Fast forward to 2013 and we find that temperature and power are still demanding requirements for MPSoC … Read More

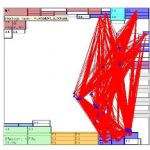

One of the challenges of physical design of a modern SoC is that of macro placement. Back when a design just had a few macros then the flooplanning could be handled largely manually. But modern SoCs suffer from a number of problems. A new white paper from Mentor covers Olympus-SOCs features to address these issues:

…

Read More

Traditionally ATPG (Automatic Test Pattern Generation) and BIST (Built-In-Self-Test) are the two approaches for testing the whole semiconductor design squeezed on an IC; ATPG requires external test equipment and test vectors to test targeted faults, BIST circuit is implemented on chip along with the functional logic of IC.… Read More

Ever sat around waiting for a time slot on the one piece of big, powerful, expensive engineering equipment everyone in the building wants to use? It’s frustrating for engineers, and a project manager’s nightmare: a tool that can deliver big results, and a lot of schedule juggling.… Read More

Social Media at Silvacoby Daniel Payne on 12-21-2013 at 4:58 pmCategories: EDA

Founded back in 1984, Silvaco has been in business for some 29 years now, focusing on the TCAD and EDA markets.

Browsing their Home page at www.silvaco.com we find four social media links in the footer: Facebook, Twitter, YouTube and LinkedIn.… Read More

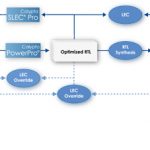

SLEC is Not LECby Paul McLellan on 12-20-2013 at 3:00 pmCategories: EDA

One of the questions that Calypto is asked all the time is what is the difference between sequential logical equivalence checking (SLEC) and logical equivalence checking (LEC).

LEC is the type of equivalence checking that has been around for 20 years, although like all EDA technologies gradually getting more powerful. LEC is … Read More

As I see the semiconductor industry going through significant changes and advances, yet ironically plagued by a growing perception that the pace of scaling is slowing, I was inclined to take a peek into what the industry experts say about the state of the industry and the future of Moore’s Law. Fortunately, at last week’s International… Read More

Is Intel About to Take Flight?