You probably remember Cadence introduced Voltus towards the end of last year at their signoff summit. This was aimed at digital designers. Prior to that they had announced Tempus, their static timing analysis tool. More recently they announced Quantus QRC extraction. All of these tools that end in -us have been re-architected… Read More

Electronic Design Automation

A Deeper Insight into Quantus QRC Extraction Solution

Last month Cadenceannounced its fastest parasitic extraction tool (minimum 5 times better performance compared to other available tools) which can handle growing design sizes with interconnect explosion, number of parasitics and complexities at advanced process nodes including FinFETs, without impacting accuracy of … Read More

Transaction-based Emulation

Verification has been going through a lot of changes in the last couple of years. Three technologies that used to be largely contained in their own silos have come together: simulation, emulation and virtual-platforms.

Until recently, the workhorse verification tool was simulation. Emulation had its place but limits on capacity… Read More

Analog Model Equivalence Checking Accelerates SoC Verification

In the race to reduce verification time for ever growing sizes of SoCs, various techniques are being adopted at different levels in the design chain, functional verification being of utmost priority. In an analog-digital mixed design, which is the case with most of the SoCs, the Spice simulation of analog components is the limiting… Read More

Speeding up IP and Data Management

IP and Data Management (DM) for SoC teams has gradually moved from ad-hoc approaches using simple Excel spreadsheets, to home-grown software that is specific to a project or company, and finally to commercially supported tools. One such commercial toolset for IP lifecycle management is from Methodics, named ProjectIC –… Read More

Layout-aware Diagnosis

Traditional test methodologies have been based on the functional model, that is to say the netlist. The most well-known is probably the stuck-at model which grades a sequence of test vectors by whether they would have managed to notice the difference between a fully functional design and one where one of the signals was permanently… Read More

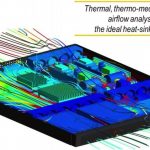

Electronic Thermal Management through Icepak

Last week my daughter was playing some games on my Google Nexus smartphone for a while when one of my friends called. When I picked up the phone, I couldn’t imagine it was so hot. There is no doubt; every electronic device today emits an order of magnitude higher heat than what it used to at most a decade ago. There is so much emphasis on … Read More

Open Source Verilog

Over the years there have been various open source EDA projects but none that has realized a full industrial strength design tool that has broad adoption and is strong enough to compete with similar products from the EDA industry.

Open source is clearly a great way to develop software. Lots of people can see all the source code and … Read More

Enabling Higher Level Design Automation with Smart Tools

Although design houses have always strived for optimizing best design flows according to their design needs by customizing the flows using effective and efficient internal as well as external tools, this need has further grown in the context of design scenarios getting wider and wider from transistor, gate and RTL to system level.… Read More

DAC Update on IC Design Tools at Mentor

On Tuesday morning I headed off to the Mentorbooth at DACfor an update on their Custom IC Design and AMS Simulation/Verification tools, Christopher Cone was the presenter. Also in the room were Jay Madiraju, and Mick from Berkeley DA.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center