You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4457

[filter] => raw

[cat_ID] => 157

[category_count] => 4457

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

Everyone has heard the expression, “Half the job is having the right tool.” In the case of FPGA-based prototyping, however, the right tool for the job is only the beginning. What teams really need to think through is what exactly should be done with an FPGA-based prototyping tool?

The obvious answer is prototyping an SoC, pre-silicon.… Read More

There is obviously a broad spectrum of semiconductor IP but broadly speaking it seems to fall into three buckets:

- foundation IP: standard cells, memories

- microprocessors and associated peripherals

- interface IP

Foundation IP is where it all started. When I was at Compass Design Automation in the 1990s that was pretty much what… Read More

SoC design these days is largely about assembling externally developed semiconductor IP with a small amount of differentiated content. Only companies who have to adopt new processes instantly develop a lot of their own IP. It makes more sense to license it. Partially because there is not a lot of differentiation in standards-based… Read More

Most engineers learn by doing, and so at DAC in June an EDA vendor with High Level Synthesis (HLS) tools held a language tutorial on choosing C++ or SystemC for design and verification projects. The EDA company is Calypto, and Stuart Clubb put together the tutorial on using synthesizable C++ or SystemC. The design and verification… Read More

Antun Domic is the GM of the Design Group at Synopsys. I sat down with him a couple of weeks ago.

His name is Croatian although, of course, there was no Croatia back then it was part of Yugoslavia. But in fact he grew up in Chile and went to university there where he studied EE and math. He came to the US as a grad student and did a PhD at MIT in … Read More

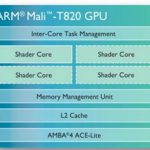

ARM is a well-known semiconductor IP provider and they often create a reference design so that SoC companies can have a starting point to work with. On the GPU side of IP the ARM engineers have an architecture called Mali, and a recent webinar hosted by Synopsys reviewed how the physical design area was minimized by using a combination… Read More

Last month in DAC I could see some of the top innovations in the EDA world. EDA is a key enabler for advances in semiconductor designs. Among a number of innovations worth mentioning (about which I blogged just after DAC), the integration of Mentor’s Veloce with ANSYS’ PowerArtist for power analysis of live applications caught my… Read More

Coventor just rolled out the latest version of SEMulator3D, their virtual fabrication tool. Very conveniently it is SEMICON West this week and they have a booth. I dropped by and got a demo from David Fried, Coventor’s CTO about all the new stuff. He’s very proud of SEMulator3D’s new logo but mostly he is proud… Read More

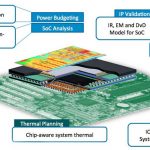

As the number of CPU, GPU, and IP is growing in an SoC, power management is becoming more and more a complex task in itself. A single tool or methodology may not be enough for complete power management and verification of an SoC. In an SoC, there can be multiple modes of operations involving hardware and software interactions, different… Read More

Only one company at the recent DAC conference and exhibit had a set of four interacting disciplines: Fluids, Structures, Electronics and Systems. Did you guess that the company was ANSYS? I get so IC focused at times that I almost forget that chips plug into boards, that boards become systems, and that systems drive and control mechanical… Read More

Solving the EDA tool fragmentation crisis