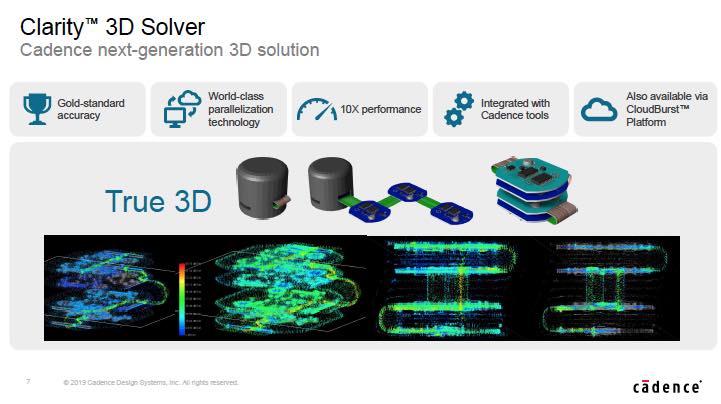

The need for full wave EM solvers has been creeping into digital design for some time. Higher operating frequencies – like those found in 112G links, lower noise margins – caused by multi level signaling such as in PAM-4, and increasing design complexity – as seen in RDL structures, interposers, advanced connector… Read More

Author: Tom Simon

Hierarchical RTL Based ATPG for an ARM A75 Based SOC

Two central concepts have led to the growth of our ability to manage and implement larger and larger designs: hierarchy and higher levels of abstraction. Without these two approaches the enormous designs we are seeing in SOCs would not be possible. Hierarchy in particular allows the reuse of component blocks, such as CPU cores.… Read More

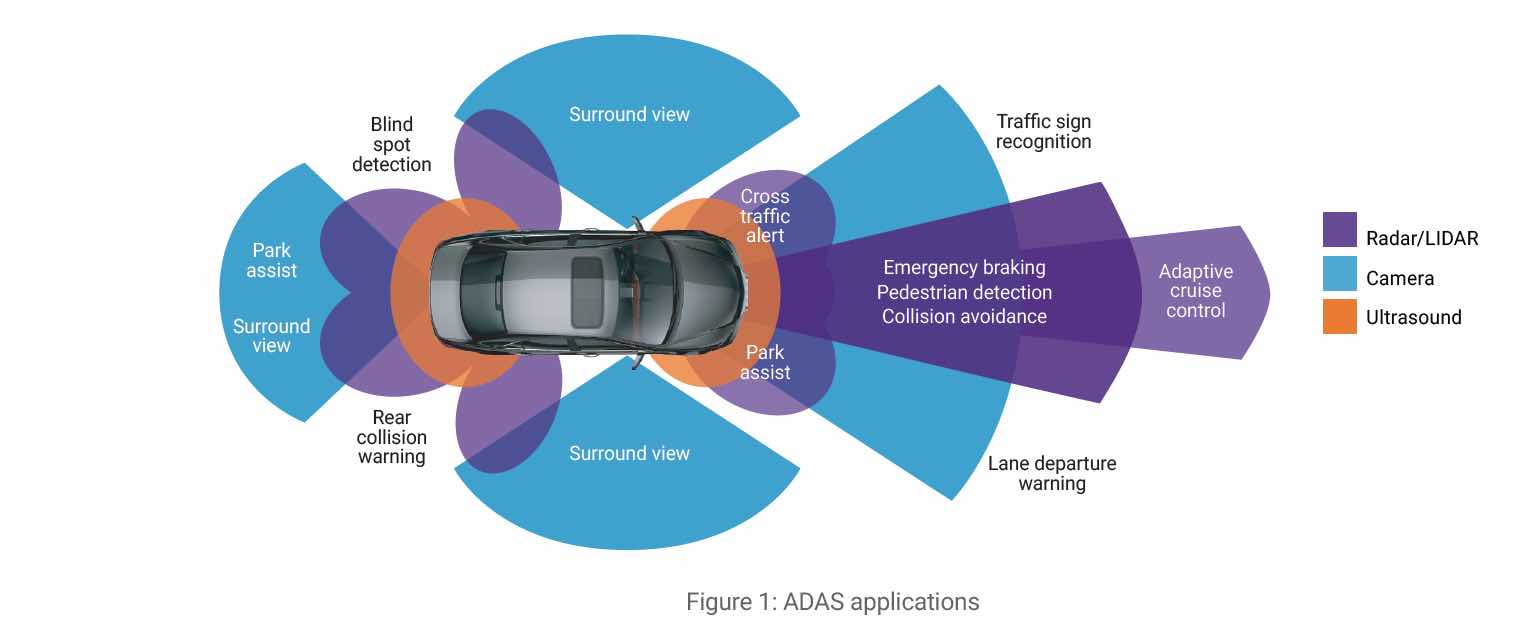

Accelerating SOC Development for Automobile Applications

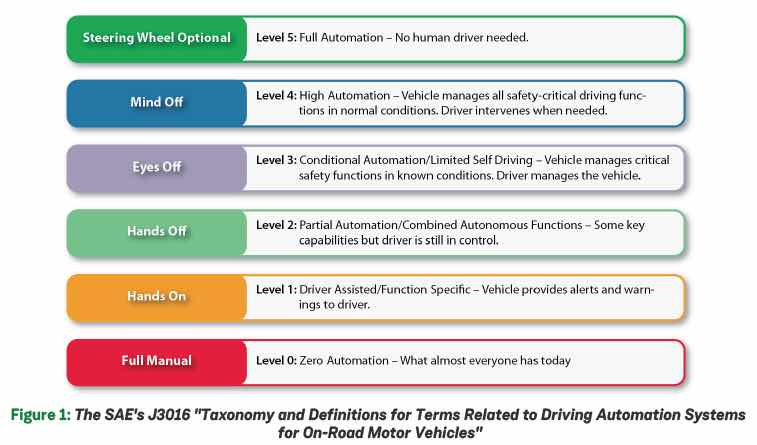

No area of electronics is moving faster than automotive semiconductors. Everyone has been talking about the increasing electronics content of automobiles for decades. With Advanced Driver Assistance System (ADAS) and autonomous driving becoming a reality the pace has picked up even more. These new designs combine just about… Read More

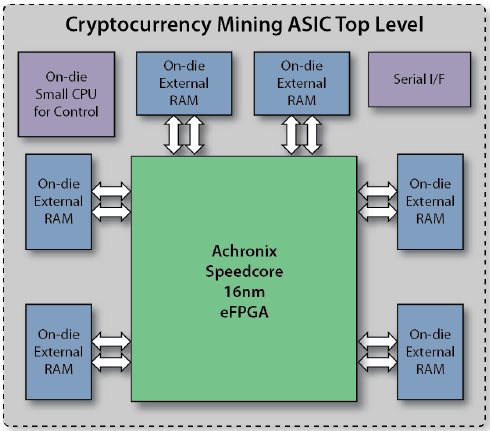

Newer cryptocurrencies highlight need for agile mining strategies

Cryptocurrencies represent a radical departure from traditional forms of money. Currencies like Bitcoin, Etherium and Monero offer many unique advantages over traditional currencies, and are changing how money is created and used. Bitcoin, the pioneer of cryptocurrencies, relies on pure computational power for so-called… Read More

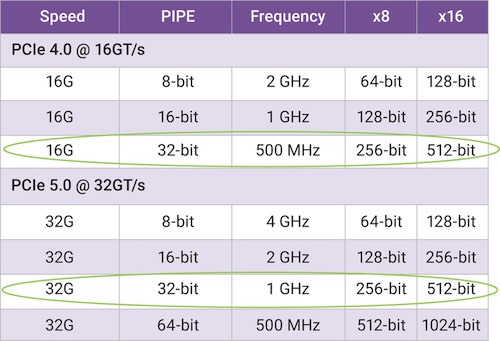

PCIe 5.0 Jumps to the Fore in 2019

2019 will be a big year for PCIe. With the approval of version 0.9 of the Base Layer for PCIe 5.0, implementers have a solid foundation to begin working on designs. PCIe 4.0 was introduced in 2017, before that the previous PCIe 3.0 was introduced in 2010 – ages ago in this industry. In fact, 5.0 is so close on the heels of 4.0, many products… Read More

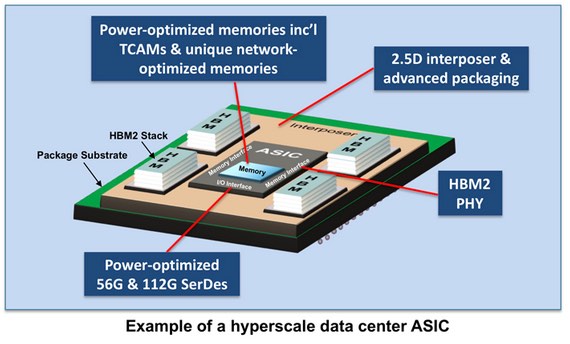

eSilicon Expands Expertise in 7nm

At SemiWiki we usually don’t write about the press releases we are sent. However, a recent press release by eSilicon caught my eye and prompted me to call Mike Gianfagna, eSilicon Vice President of Marketing. The press release is not just about one thing, rather it focuses on a number of interesting things that together show their… Read More

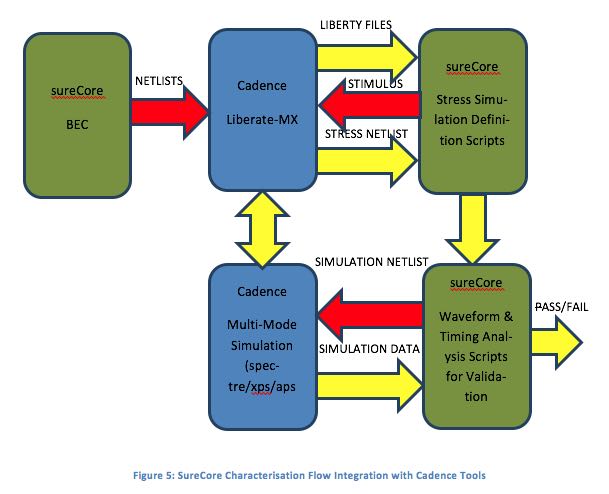

Low Power SRAM Complier and Characterization Enable IoT Applications

If you are designing an SOC for an IoT application and looking to minimize power consumption, there are a lot of choices. However, more often than not, looking at reducing SRAM power is a good place to start. SRAMs can consume up to 70% of an IC’s power. SureCore, a leading memory IP supplier, offers highly optimized SRAM instances … Read More

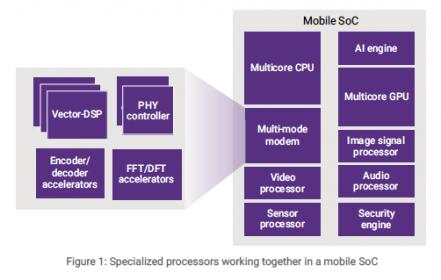

Goldilocks Solution for SOC Processors

SOC designers face choices when it comes to choosing how to implement algorithms in their designs. Moving them to hardware usually offers advantages of smaller area, less power and faster processing. Witness the migration of block chain hashing from CPUs to ASICs. However, these advantages can come with trade-offs. For one, … Read More

GLOBALFOUNDRIES Talks About Enabling Development of 5G ICs

5G is in the news again. Sprint has mounted a legal challenge against ATT, claiming that ATT is misleading people into believing that they already are offering 5G. While ATT is about to start testing of 5G, they have also sent out updates that causes customer phones to display 5GE when they are still on 4G LTE systems. The truth is that… Read More

Building Better ADAS SOCs

Ever since we replaced horses in our personal transportation system, folks have been pining for cars that offer some relief from the constant need for supervision, control and management. Indeed, despite their obvious downsides, horses could be counted on to help with steering and obstacle avoidance. There are even cases when… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry