Speaking of having the right tools, FPGA-based prototyping has become as much if not more about the synthesis software than it is about the FPGA hardware. This is a follow-up to my post earlier this month on FPGA-based prototyping, but with a different perspective from another vendor. Instead of thinking about what else can be done… Read More

Author: Don Dingee

Taking prototyping beyond prototypes

Everyone has heard the expression, “Half the job is having the right tool.” In the case of FPGA-based prototyping, however, the right tool for the job is only the beginning. What teams really need to think through is what exactly should be done with an FPGA-based prototyping tool?

The obvious answer is prototyping an SoC, pre-silicon.… Read More

Xilinx in an ARM-fueled post-Altera world

When the news broke about the on, off, and on-again Intel-Altera merger a few weeks ago, I checked off another box on my Six Degrees of Kevin Bacon scorecard. That plus a $5 bill gets me a Happy Meal at McDonalds, but in a post-Altera world, it might be worth more.

On January 16, 2008, I’m sitting in a meeting with some Intel strategic marketing… Read More

DDR stands for Don’t Do (Just) RTL

In optimizing SoC design for performance, there is so much focus on how fast a CPU core is, or a GPU core, or peripherals, or even the efficiency of the chip-level interconnect. Most designers also understand selecting high performance memory at a cost sweet spot, and optimizing physical layout to clock it as fast as possible within… Read More

5 Things Chipmakers Are Missing on the IoT

When the RISC movement surfaced in 1982, researchers analyzed UNIX to discover what instructions multi-user code was actually using, and then designed an instruction set and execution pipeline to do that better. Fewer instructions meant fewer transistors, which led to less power consumption – although in the original… Read More

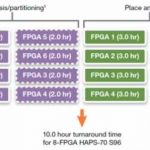

Aldec packs 6 UltraScale parts on HES-7

A few months ago, when the Xilinx UltraScale VU440 FPGA began shipping, one of the immediate claims was a quad-FPGA-based prototyping board touted as “Godzilla’s Butcher on Steroids”. That was a refreshing and creative PR approach, frankly. I’m always careful with less creative terms like “world’s biggest” or “world’s fastest”,… Read More

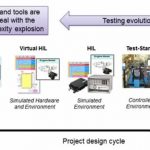

Virtual HIL and the 100M LOC car

Aerospace and defense applications have traditionally leveraged hardware-in-the-loop (HIL) testing to overcome several issues. A big one is how expensive the physical system is. Even breaking down the system into subsystems for test can still be too expensive when fielding more than a couple test stations. Modeling elements… Read More

NFV opens gate for ARM server stampede

A couple of years ago, our own Paul McLellan gave us a report on the 2013 Linley Microprocessor Conference with a provocative headline: “Server Shift to ARM Becomes a Stampede”, a title right off one of the Linley slides. 64-bit ARMv8 architecture was relatively new to the game, and ARM share in networking platforms was just a sliver… Read More

Breaking the SoC lab walls

There used to be this thing called the “computer lab”, with glowing rows of terminals connected to a mainframe or minicomputer. Computers required a lot of care and feeding, with massive cooling and power requirements. Microprocessors and personal computers appeared in the 1970s, with much smaller and less expensive machines… Read More

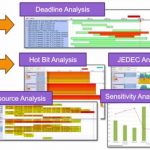

New Vivado release goes from Lab to UltraScale

Xilinx users will welcome the brand-new release of Vivado Design Suite 2015.1. For openers, device support for the latest FPGAs in the UltraScale family – XCVU440, XCVU190, and XCVU125 – has been added in the release, and early access code for the XCVU160 is available from a local Xilinx FAE. Installation has been streamlined, … Read More

Solving the EDA tool fragmentation crisis