The year is now 1991 and in search for a more peaceful life we decided to move to Canada. At that time, very few companies had advanced flows in VLSI but Ottawa having BNR, Northern Telecom, Mitel, etc., looked to be the most promising place. After a few hiccups in finding a job, I landed in MOSAID, a small company with35 people at that … Read More

Tag: virtuoso

Cadence Expands Integrated Photonics Beachhead

In November of 2016, I made a bold statement that October 20, 2016 would stand as a watershed day in integrated photonics. The reason for this claim was that GLOBALFOUNDRIES proclaimed that integrated photonics was real and here to stay. The same week I wrote an article about Cadence Design Systems securing a photonic beachhead … Read More

Qorvo Uses ClioSoft to Bring Design Data Management to RF Design

A couple weeks ago I gave a heads-up about a webinar that was being hosted by ClioSoft, Qorvo and Keysight. The topic of the webinar was how to manage custom RF designs across multiple design teams and CAD flows. The webinar was held on February 1st and included presentations by Marcus Ray of Qorvo and Michele Azarian of Keysight.

Much… Read More

Fabless Photonic Design Flow Takes Shape as Cadence teams up with Lumerical and PhoeniX

This week Cadence Design, Lumerical Solutions and PhoeniX Software hosted a two-day photonic summit and workshop. The first day had nearly 100 registered participants and featured industry leaders from Global Foundries, UCSB, MIT, Hewlett Packard Enterprise, General Electric, Boeing, Rockley Photonics, and Juniper Networks… Read More

Getting Low Power Design Right in Mixed Signal Designs

Mixed-signal design creates all sorts of interesting problems for implementation and verification flows, particularly when it comes to design for low power. We tend to think of mixed-signal as a few blocks like PLLs, ADCs and PHYs on the periphery of the design. Constrain and verify the digital power requirements up to analog … Read More

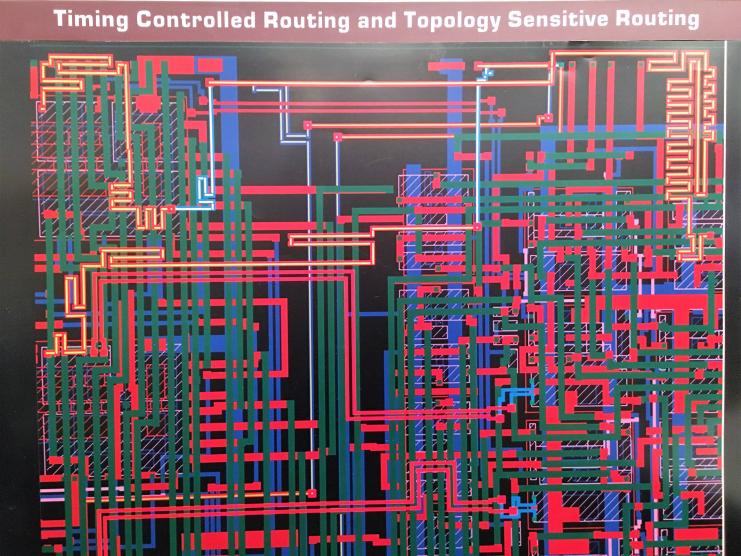

Explore Your Interconnect the ICScape Way

One of the surprises at DAC for ICScape was to be listed on Gary Smith’s list of companies to see. Surprised, since ICScape had never presented their products to him. They were listed under design debug. They don’t have a single product that really falls under that description, but rather a family of tools under the ICExplorer… Read More

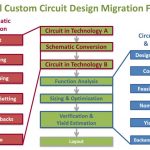

How MunEDA Helps Solve the Difficulties of AMS/RF IP Reuse

Reusing design IP is crucial for competitiveness. The need for reuse occurs with new designs on the same process node as the original design, new designs at the same node but using a different PDK or foundry, or designs on a different process node – usually smaller. However, achieving effective IP reuse has always been a challenge.… Read More

Tackling Layout Gradient Effects in 16 nm FinFET using Layout Automation

My first exposure to automating IC layout was back in the 1980’s at Intel where I coded a layout compiler to auto-generate about 6% of a graphics processor chip. The need to use automation for IC layout continues today, and with the advent of FinFET technology there are some new challenges like layout gradient effects that … Read More

What makes the world smart?

The simple answer is when everything in the world is smart. But if you think deeply, you would find that the continuous progression to make things easy in life is what makes the world smarter day-by-day – the sky is the limit. In the world of computing, consider the 17[SUP]th[/SUP] century era when humanbrain was used as a computer … Read More

How ST Designs with Layout Dependent Effects (LDE)

I first visited STat their Agrate, Italy site where Flash memory development is done. At DACthis year Antonio Bogani talked about how ST designs with LDE while using EDA tools and a PDK (Process Design Kit) from Cadence. They recorded the 17 minute presentation, and you can view it herewithout having to register. Antonio’s… Read More