When it comes to debugging a design testbench organized in object-oriented style with objects, component hierarchies, macros, transactions and so on, it becomes an onerous, tasteless, and thankless task for RTL verification engineers who generally lag in software expertise. Moreover, class-based debugging tools have lagged… Read More

Tag: uvm

Experts Talk at Mentor Booth

It’s less than four weeks to go at DAC 2015 and the program is final now. So I started investigating new technologies, trends, methodologies, and tools that will be unveiled and discussed in this DAC. In the hindsight of the semiconductor industry over the last year, I see 14nm technologies in the realization stage and 10nm beckoning… Read More

Successful Venture of an Indian Global VIP Company

It’s rare that we find a truly Indian-based company operating globally in the semiconductor space. Although the ‘gold rush’ towards IP development in the last decade initiated many IP start-ups in India, today we rarely find Indian IP company names which are shining in the global arena. The story of services companies is different,… Read More

UVM Debugging Made Easy & Productive in Questa

As design complexity and size is increasing, SoC verification has become one of the most difficult and time consuming tasks in the design closure.UVM (Universal Verification Methodology, an accellera initiative) is one of the best verification methodologies that support common language, coherent strategy, clarity and transparency… Read More

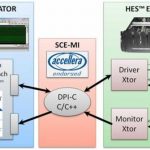

Aldec increasing the return on simulation

Debate rages about which approach is better for SoC design: simulation, or emulation. Simulation proponents point to software saving the need for expensive hardware platforms. Emulation supporters stake their claims on accuracy and the incorporation of real-time I/O. A few years back, some creative types coined the term SEmulation,… Read More

Ensuring Safety Distinctive Design & Verification

In today’s world where every device functions intelligently, it automatically becomes active on any kind of stimulus. The problem with such intelligence is that it can function unfavorably on any kind of bad stimulus. As the devices are complex enough in the form of SoCs (which at advanced process nodes are more susceptible to … Read More

HLS – Major Improvement through Generations

I am a believer of continuous improvement in anything we do; it’s pleasant to see rapid innovation in technology these days, especially in semiconductor space – technology, design, tools, methodologies… Imagine a 100K gates up to 1M gates design running at a few hundred MHz frequency and at technology node in the range of .18 to … Read More

Designing Hardware with C++ and its Advantages

Very recently, I was seeing intense discussions on the need for agile hardware development just like agile software and ideas were being sought from experts as well as individuals. While in software world it has already evolved, in hardware world it’s yet to see the shift in paradigm. My point is that the end goal of agile hardware… Read More

Design & EDA Collaboration Advances Mixed-Signal Verification through VCS AMS

Last week it was a rare opportunity for me to attend a webinar where an SoC design house, a leading IP provider and a leading EDA tool provider joined together to present on how the tool capabilities are being used for advanced mixed-signal simulation of large designs, faster with accuracy. It’s always been a struggle to combine design… Read More

Vlang – Opportunities Galore for Productivity & Performance

Yes, verification technologies are open to innovation for improved productivity and performance in the face of ever growing SoC/IP design sizes and complexities. There is not much scope left in processor speed to improve, other than multi-core processors in servers which again need software properly architected to be thread-able… Read More