You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

A single bug on a full-chip SoC can pull engineers off roadmap work for days or even weeks. It involves massive waveforms, thousands of files of RTL and UVM, and dense specs that aren’t always perfect. Finding these bugs have always been a matter of engineer-hours and how well knowledge diffuses through the organization.

Bronco … Read More

By Vikash Kumar, Senior Verification Architect | Arm | IEEE Senior Member.

The Problem Every Verification Engineer Recognizes

You ask an LLM to generate a UVM testbench. It produces 25 files. Everything compiles. You run the simulation — and nothing happens. The scoreboard reports zero checks. The slave driver stops after 10… Read More

Verification has become the dominant bottleneck in modern chip design. As much as 70% of the overall design cycle is now spent on verification, a figure driven upward by increasing design complexity, compressed schedules, and a chronic shortage of design verification (DV) engineering bandwidth. Modern chips generate thousands… Read More

Recently, I reported on my conversation with Cristian Amitroaie, CEO of AMIQ EDA, about automated generation of documentation from design and verification code. Before we chose that topic for a post, Cristian described several capabilities of the AMIQ EDA product family that might be of interest to design and verification engineers.… Read More

At times it has seemed like any development in EDA had to build a GenAI app that would catch the attention of Wall Street. Now I see more attention to GenAI being used for less glamorous but eminently more practical advances. This recent white paper from Siemens on how to help verification engineers get up to speed faster with PSS is … Read More

Key Takeaways

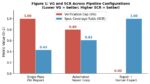

– High-Level Synthesis (HLS) delivers not only design productivity and quality but also dramatic gains in verification speed and debug – and it delivers them today.

– Rise Design Automation uniquely enables SystemVerilog-based HLS and SystemVerilog verification, reusing proven verification… Read More

Hardware designers have been using RTL and hardware description languages since the 1980s, yet many attempts at moving beyond RTL have tried to gain a foothold. At the #62DAC event I spent some time with Mike Fingeroff, the Chief High-Level Synthesis Technologist to understand what his company Rise Design Automation is up to. … Read More

The 2025 Design and Verification Conference (DVCon) was a four-day event packed with insightful discussions, cutting-edge technology showcases, and thought-provoking debates. The conference agenda included a rich mix of tutorial sessions, a keynote presentation, a panel discussion, and an exhibit hall with Electronic… Read More

In the early days of the PSS rollout, some verification engineers were suspicious. Just as they were beginning to get comfortable with UVM, here came yet another standard to add to their learning and complexity overhead. Then the fog started to clear; UVM is ideal for block-level testing whereas PSS is ideal for system level testing.… Read More

You begin writing some UVM code and there are parts of the code that aren’t done yet, so you begin to use uvm_objection, guarding that code. Rich Edelman, a product engineer at Siemens doing verification debug and analysis, wrote a paper on this topic, which I just read. This blog covers the topic of objections and provides some different… Read More