When technology advances, complexities increase and data size becomes unmanageable. Fresh thinking and a new environment for automation are needed to provide the required increase in productivity. Specifically in case of circuit simulation of advanced-node analog designs, where precision is paramount and a large number… Read More

Tag: mixed signal

Mass customization coming to MEMS?

With the industry abuzz about the Apple purchase of a Maxim Integrated fab as a potential R&D facility for MEMS design, it begs the question: is creating a MEMS device that easy?

MEMS technology is approaching the same fork in the road where digital design encountered LSI four decades earlier. … Read More

Optimizing power for wearables

I was at the Cadence front-end summit this week; good conference with lots of interesting information. I’ll start with a panel on optimizing power for wearables. Panelists were Anthony Hill from TI, Fred Jen from Qualcomm, Leah Clark from Broadcom and Jay Roy from Cadence. Panels are generally most entertaining when the panelists… Read More

Automotive MCU code fault-busting with vHIL

With electronic and software content in vehicles skyrocketing, and the expectations for flawless operation getting larger, the need for system-level verification continues to grow. Last month, we looked at a Synopsys methodology for virtual hardware in the loop, or vHIL… Read More

Can FD-SOI Change the Rule of Game?

It appears so. Why there is so much rush towards FD-SOI in recent days? Before talking about the game, let me reflect a bit on the FD-SOI technology first. The FD-SOI at 28nm claims to be the most power-efficient and lesser cost technology compared to any other technology available at that node. There are many other advantages from… Read More

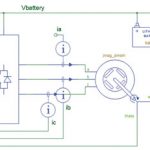

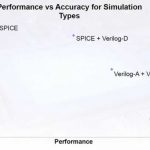

Verilog-AMS connects T-SPICE and Riviera-PRO

With advances in available IP, mixed signal design has become much easier. Mixed signal verification on the other hand is becoming more complicated. More complexity means more simulation, and in the analog domain, SPICE-based techniques grinding away on transistor models take a lot of precious time. Event-driven methods like… Read More

Cadence Mixed Signal Technology Forum

Yesterday was Cadence’s annual mixed-signal technology forum. I think that there was a definite theme running through many of the presentations, namely that wireless communication of one kind or another is on a sharp rise with more and more devices needing to connect to WiFi, Bluetooth and so on. This was most obvious during… Read More

Designing SmartCar ICs

When I upgraded cars from a 1988 to 1998 Acura it seemed like my car had become much smarter with a security chip in the key, security codes in the radio and a connector for computer diagnosis, however in today’s modern auto there’s a lot more mixed-signal design content. Micronasand Synopsysgot together and hosted … Read More

180nm still a big deal

When I was reading the recent Daniel Payne article “Designing Change Into Semiconductor Techonomics” with commentary on a recent presentation from Aart de Geus of Synopsys, one chart jumped out at me: the most popular process node for new design starts today is 180nm.

Upon mentioning that to a few of my IoT counterparts, they quickly… Read More

Mark your Date for Semiconductor Design Vision

A very popular acronym is ‘WYSIWYG’ – What You See Is What You Get! This is very true and is important to visualize things to make it better in various aspects such as aesthetics, compactness, organization, structure, understandable for correction and so on; the most important, in case of semiconductor design, is being able to identify… Read More