In an ANSYS seminar held at DesignCon 2019, Dr. Larry Williams, ANSYS Director of Technology, outlined how 5G design innovation can be accelerated through simulation. He posited that 5G will become a general-purpose technology that affects an entire economy, drastically alter societies and unleash a cascade of complementary… Read More

Tag: mixed signal

Designing a fully digitally controlled DC-DC buck converter

One of the unsung heroes of our digital world is the modest voltage converter. Batteries and wired power sources rarely match up with the supply needs for advanced ICs. Leading edge ICs have multiple voltage domains and very often, as in the case of processors, use dynamic voltage scaling to help conserve power. Looking at where … Read More

Qorvo and KeySight to Present on Managing Collaboration for Multi-site, Multi-vendor RF Design

Over the last several weeks I’ve been having a lot of discussions with colleagues around IP reuse and design data management. This led me to a discussion with Ranjit Adhikary, Marketing Vice President for ClioSoft.

ClioSoft is best known for their design collaboration software platform called SOS. They also sell an enterprise… Read More

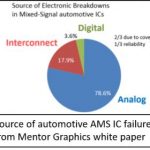

Mentor DefectSim Seen as Breakthrough for AMS Test

For decades, digital test has been fully automated including methodologies and automation for test pattern generation, grading and test time compression. Automation for analog and mixed-signal (AMS) IC test has not however kept pace. This is troubling as according to IBSapproximately 85% of SoC design starts are now AMS designs.… Read More

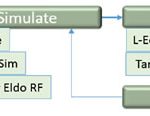

Can one flow bring four domains together?

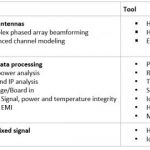

IoT edge device design means four domains – MEMS, analog, digital, and RF – not only work together, but often live on the same die (or substrate in a 2.5D process) and are optimized for power and size. Getting these domains to work together effective calls for an enhanced flow.

Historically, these domains have not played together … Read More

3 Small-Team Design Productivity Challenges Managed

“Data management tools? We use small teams doing small designs. Each project only has two or three designers. Everyone uses the same EDA tools. Why do we need another tool for collaboration?” Good question. If you enjoy frequent meetings and redoing work because someone didn’t understand the status of IP blocks, the answers may… Read More

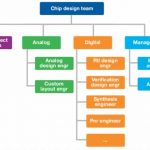

Organizing Data is First Step in Managing AMS Designs

Efficient collaboration is essential to meeting tight chip design schedules. In analog and mixed signal (AMS) design, collaboration has many facets. Design tools are usually specific to roles, and handoffs are numerous, especially when moving a design to a foundry. … Read More

Customized PMICs with OTP in automotive and IoT

Power. Every device needs it. Managing it properly can make all the difference between a device people enjoy using and one that is more hassle than it is worth. What happens between the battery and the processor is the job of the power management integrated circuit (PMIC).

Why are PMICs gaining so much attention? Increased power … Read More

Webinar Alert – Helping Mixed Signal not be Mixed Up

Today’s profound statement: “don’t fall in love with your tools, figure out the biz process change first.” Mixed-signal SoC designers are having ample challenges with their design process and are in need of design management, but don’t want another tool to do it.… Read More

One transistor for the future of mmWave?

We’ve heard recently from several sources that millimeter wave radios, once the exclusive realm of defense and satellite use, are now finding homes in applications such as automotive radar and 5G networks. Therein lies a significant opportunity for digital design: moving frequency conversion and filtering from the analog … Read More