The integration of artificial intelligence (AI) into Electronic Design Automation (EDA) is revolutionizing chip design, addressing the critical shortage of skilled engineers and accelerating the development process. As Jeff Dyck, Senior Director of Engineering at Siemens EDA, explains in a recent DACtv presentation, … Read More

Tag: fastspice

Podcast EP221: The Importance of Design Robustness with Mayukh Bhattacharya

Dan is joined by Mayukh Bhattacharya, Engineering, Executive Director, at Synopsys. Mayukh has been with Synopsys since 2003. For the first 14 years, he made many technical contributions to PrimeSim XA. Currently, he leads R&D teams for PrimeSim Design Robustness and PrimeSim Custom Fault products. He was one of the early… Read More

INTERCHIP achieves 3x faster verification for next-gen clocking oscillator with advanced analog and mixed-signal EDA technology

Customer case studies have always been my favorite source of information. Press releases are a great start but there is always more to the story. Fortunately, I had the opportunity to speak with Sumit Vishwakarma, principal product manager at Siemens EDA about their recent press release with Interchip. I was an advisor to Berkeley… Read More

Synopsys Debuts Major New Analog Simulation Capabilities

Just prior to this year’s Synopsys User Group (SNUG) meeting, I had a call with Hany Elhak, Group Director of Product Management and Marketing at Synopsys, to talk about their latest announcements for analog simulation. Synopsys usually has big things to talk about each year around this time – this year is no exception. Hany… Read More

Free Webinar on SPICE Simulation

The world of SPICE simulators is one filled with compromises. Typically, it is possible to choose the highest accuracy and pay a performance and capacity penalty, or to choose high speed and capacity but give up accuracy in the process. Many semiconductor companies have been turning to Primarius Technologies to help escape these… Read More

Creating Analog PLL IP for TSMC 5nm and 3nm

TSMC’s Open Innovation Platform’s main objective is to create and promote partnership for producing chips. This year’s OIP event included a presentation on the joint efforts of Silicon Creations, Mentor, a Siemens business and TSMC to produce essential PLL IP for 5nm and 3nm designs. The relentless push for smaller geometries… Read More

Webinar on TFT and FPD Design

I knew that the acronym for TFT meant Thin Film Transistors, but I hadn’t heard that FPD stands for Flat Panel Detectors. It turns out the FPD are solid-state sensors used in x-ray applications, similar in operation to image sensors for digital photography and video. I’ll be attending and blogging about what I learn… Read More

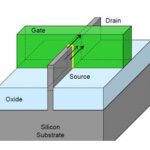

How 16nm and 14nm FinFETs Require New SPICE Simulators

About 35 years ago the first commercial SPICE circuit simulators emerged and they were quickly put to work helping circuit designers predict the timing and power of 6um NMOS designs. Then we had to limit our circuit simulations to just hundreds of transistors and interconnect elements to fit into the RAM and complete simulation… Read More

Analog FastSPICE Update at DAC

Tuesday night over dinner at DAC I was able to chat with Ravi Subramanian, CEO of Berkeley DA, recently acquired by Mentor Graphics back on March 21st. This acquisition provided Mentor with an Analog FastSPICE circuit simulator to round out its collection of simulators.… Read More

AMS Verification and Regression Testing of SoC Designs

Digital verification engineers on SoC designs have adopted many techniques to help ensure first silicon success: using compiled simulators, constrained random test, simulation farms, SystemVerilog methodology, and self-checking testbenches. AMS verification has tended to be ad-hoc or sharply divided into separate analog… Read More