Successful ASIC providers offer top-notch infrastructure and methodologies that can accommodate varied demands from a multitude of customers. Such ASIC providers also need access to best-in-class IP portfolio, advanced packaging and test capabilities, and heterogeneous chiplet integration capability among other things. Of course, to deliver the above in a viable fashion, the provider needs to pick a focus in terms of what markets it serves. Alchip chose the high-performance markets for its dedicated focus many years ago and has stayed the course. As of last year, more than 80% of its $372M revenue was derived from high performance computing (HPC) related markets.

Prior posts on SemiWiki have spotlighted many of Alchip’s capabilities and accomplishments. Here is one of the latest achievements by Alchip for which it collaborated with Synopsys. Alchip delivered a TSMC 7nm process-based SoC capable of 2.5GHz performance, consuming less than 400 watts of dynamic power on a 480 sq.mm die. Such a performance, power, area (PPA) metric on an AI-enabled data center SoC is noteworthy, with particular attention to be paid to the 400 watts power number.

AI-enabled Data Center SoC

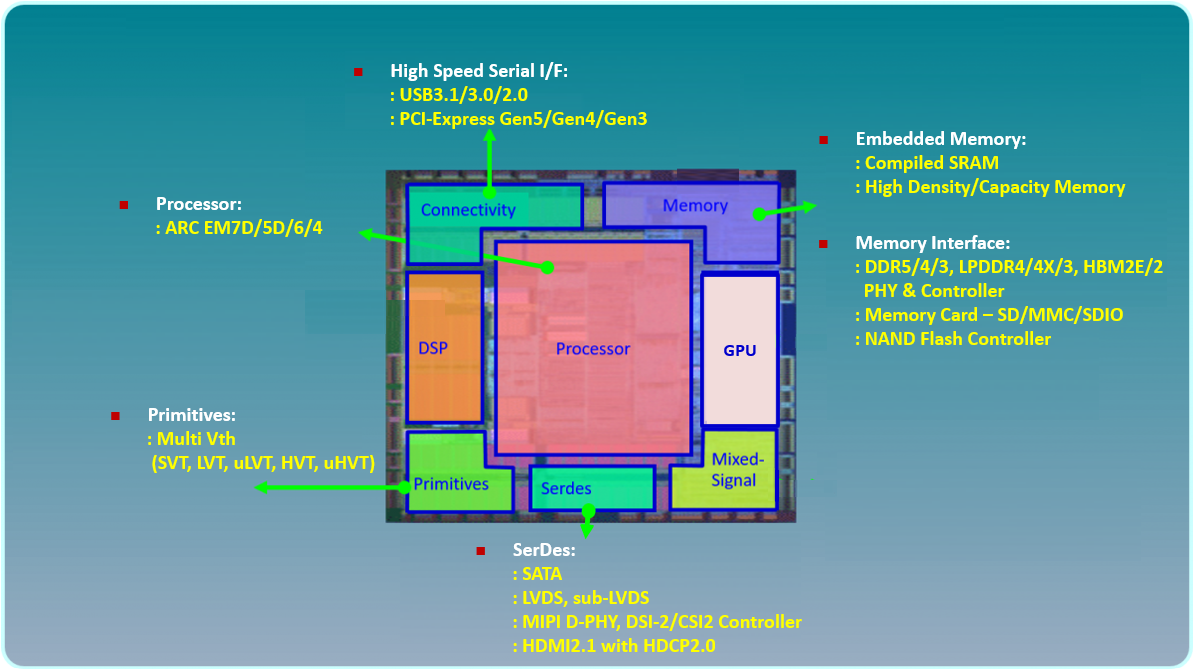

A high-level block diagram of the Alchip implemented SoC (see below) showcases the complexity and highlights the need for a collaborative, multi-company effort.

Of course, for the above SoC which is data center oriented, memory and I/O operations consume an even higher percentage of the total chip power consumption.

With HPC data centers handling increasingly large data sets, memory and other high-speed I/O operations reach extreme levels, leading to elevated thermal conditions inside the server rooms. In addition to the cooling mechanisms deployed within server rooms, lower thermal dissipation from data center chips will go a long way in keeping thermal levels under control. 400 watts of power dissipation is a pretty aggressive target for a data center chip, which in turn calls for aggressively reducing the power consumed by memory and other I/Os.

Alchip-Synopsys Collaboration

A number of members of the TSMC Open Innovation Platform (OIP) teamed up on the AI-Enabled Data Center SoC project, with Synopsys EDA tools, foundation IP and interface IP bringing a lot to bear.

Synopsys offers the broadest portfolio of IP across TSMC technology nodes ranging from 180nm to 3nm FinFET through its continuous innovation cycle for optimizing SoC PPA. Alchip leveraged Synopsys IP portfolio including its optimized cell set tailored for HPC market applications. Included with the IP set are memory design for testability (DFT) and power management support.

Standby Power

Synopsys memory compilers are optimized for power hungry applications: memory standby power is reduced by up to 50% in light sleep mode, by up to 70% in deep sleep mode and by up to 95% in shut down mode.

Switching Power

Clock power is a significant component of a chip’s total power. Through a fully automated multibit-mapping flow from the RTL stage, Synopsys was able to reduce clock power by more than 30%, resulting in more than 19% reduction of the total power. The optimization techniques involved mapping sequential multibits to combinational multibits through De-Banking and Re-Banking.

Optimized Cell Set

Low active power versions of the combinational cells helped reduce dynamic power significantly. Special wide muxes, compressors and adders helped minimize routing congestion and total power. Fast adders help ensured performance was met post route.

PPA Benefits

In addition to reducing power, multibit combinational cells also reduced area. The logic restructuring done as part of optimization techniques reduced congestion to achieve better timing. Flops optimized for Setup/Hold enabled faster timing closure.

Summary

Alchip met its cloud-infrastructure customer’s PPA challenge through its tight collaboration with Synopsys. For Alchip’s press release on this, visit here. With the TSMC N7 based SoC success under its belt, the partners are working together on TSMC N5 and TSMC N3 engagements. For more details contact Alchip.

Also Read:

Alchip Technologies Offers 3nm ASIC Design Services

Alchip Reveals How to Extend Moore’s Law at TSMC OIP Ecosystem Forum

Share this post via:

Comments

2 Replies to “Achieving 400W Thermal Envelope for AI Datacenter SoCs”

You must register or log in to view/post comments.