Throughout its history, the ASIC industry has had its ups and downs. With feast and famine cycles, the ASIC business model is not for the faint of heart. Some companies tread boldly while others dread the cycles and stay away from this business model. Those who are consistently successful have to overcome many challenges thrown at them. This in turn requires focused dedication to the model and ongoing strategic investments to stay on top. ASIC companies stay consistently successful by judiciously overcoming the many challenges thrown at them.

ASIC Business Model Challenges

Supply Chain

In a sense, it was easier when ASIC companies were vertically integrated with their own foundries. Not only did they gain early access to the latest process technology details, all their customers’ wafer volume aggregated to the same foundry as well. This is no longer the case, with ASIC companies having to tap third party foundries. And this points extends to other parts of the supply chain too.

Customers

In addition to the PPA benefits of an ASIC, customers go the ASIC route for advantageous pricing compared to choosing an ASSP. It is interesting to highlight that the term ASIC itself is a misnomer. The product is a customer-specific product targeted toward an application. Naturally, every customer is likely going to aggressively push the ASIC provider in non-overlapping ways on both technical and commercial aspects.

Alternate Solutions

While technically many products could benefit from an ASIC implementation, depending on the end market and the commercial terms for an ASIC, customers may choose an alternate non-ASIC solution. For example, customers may be willing to go an ASSP, FPGA or a GPU route to save on the upfront NRE investment and/or design cycle time and time to market. This is one of the things that happens on a regular basis and certainly when the ASIC market goes through the famine part of the feast-famine cycle.

Strategic Investments

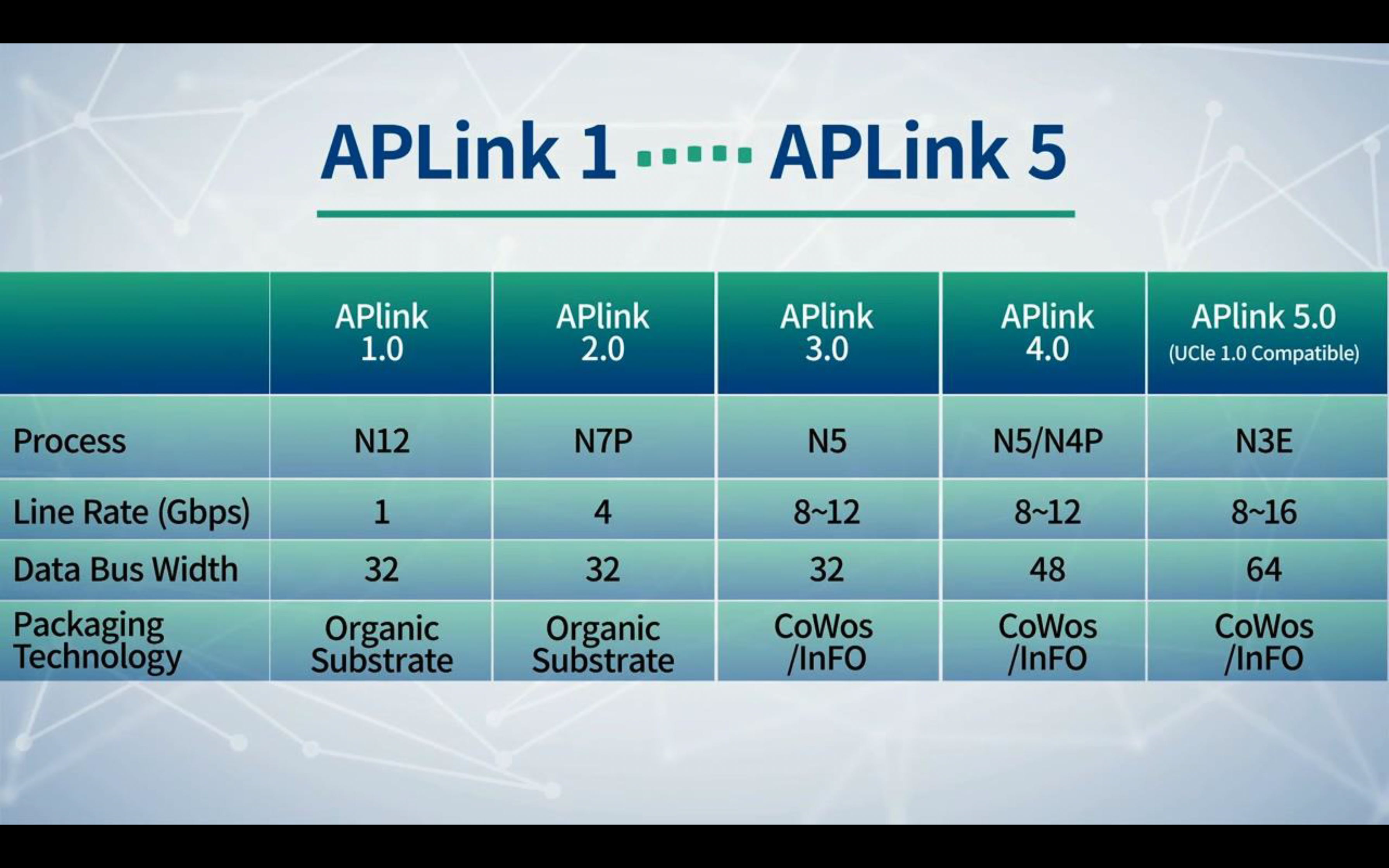

Significant design capabilities and infrastructure investments are expected off of ASIC providers to support HPC, cloud computing, edge computing, AI, automotive and other applications. With the slowing down of Moore’s law benefits on advanced process nodes, large monolithic chips are giving way to chiplet based implementations. With chiplets, one can have the best of both worlds. Leading edge process for some chiplets and main stream/trailing edge process for others. An ASIC provider will be faced with supporting heterogeneous chiplets integration. Investments in developing capabilities and methodologies to support 2.5/3D packaging and high-speed Die-to-Die interfacing are critical to keep up with the trends. Being involved in standardization efforts such as the Universal Chiplet Interface Express (UCIe) is critical.

Design Technology and Infrastructure

Whether an ASIC or an ASSP, PPA, cost, and time to market are the lowest common denominator requirements. Accordingly, design service organizations hone their design technology, methodology and infrastructure on an ongoing basis. The added challenge for ASIC design service organizations is that different customers are going to stress their infrastructure differently. For example, clock methodology that may yield optimal results on one customer’s chip may yield sub-optimally on another customer’s chip, impacting performance. The P&R methodology may run into different issues depending on the chip and thereby impacting die size. And so on. All of these impact time to market for the customer and revenue and profitability impact for both the customer and the ASIC provider.

Consistently successful ASIC providers have top-notch infrastructure and methodologies that can accommodate varied demands from multitude of customers.

Success Requires Focused Dedication

For overcoming the challenges described in the above section and the business model challenges section, a successful ASIC company needs:

- Robust yet flexible design methodology

- Flexible engagement model (both commercial and technical)

- Best-in-class IP portfolio (access to third-party IP and in-house IP/customization)

- Heterogenous chiplet integration capability

- Advanced packaging and test capabilities

In order to deliver all of the above in a viable manner, one needs to pick a focus in terms of what markets they serve.

Alchip Treads Boldly

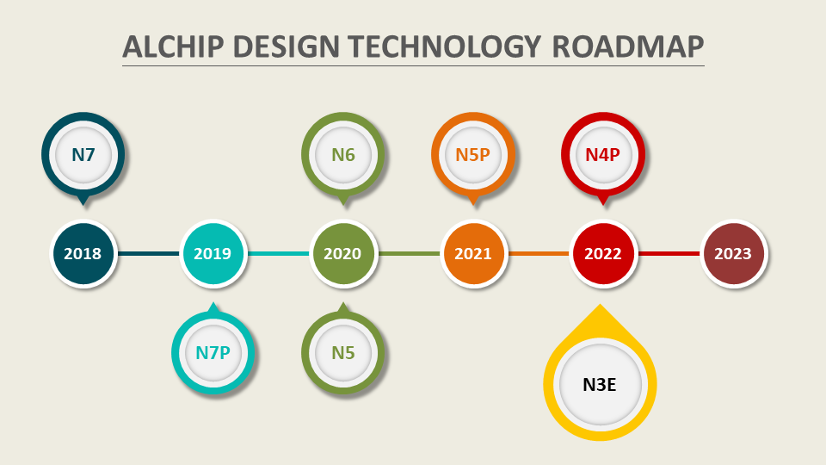

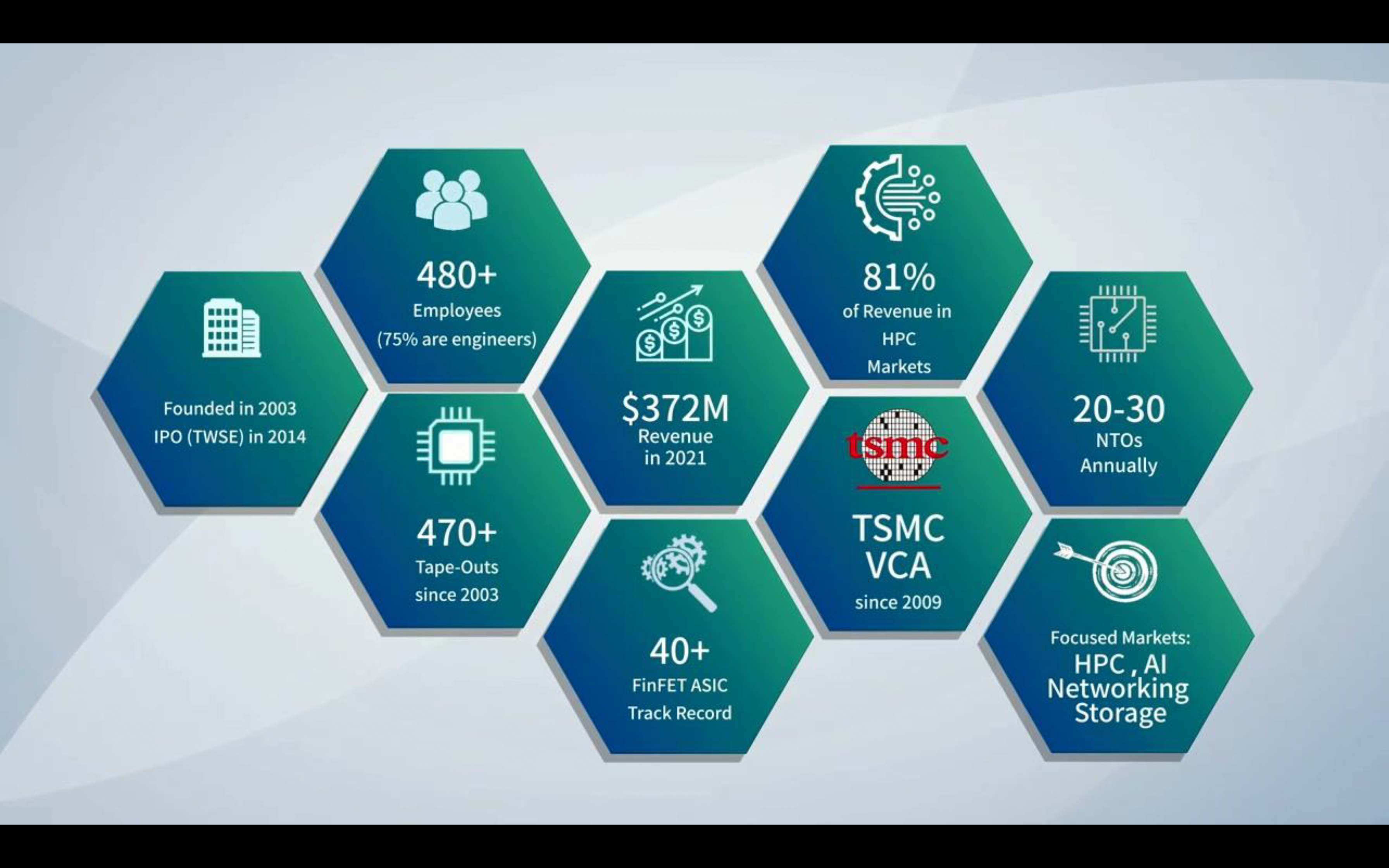

Alchip picked the high-performance markets as their dedicated focus many years ago and stayed the course. They have made strategic investments to stay with the trends and developed design technology and infrastructure to service their customers. Their dedication has yield everything that is identified in the above section. Alchip has consistently stayed on top of supporting the latest process nodes from TSMC, the leading foundry. Not only have they developed capability to support 2.5D/3D packaging in general but also been qualified to support TSMC’s CoWoS packaging technology. They had developed APLink family of Die-to-Die interface IP to support chiplets integration well before the UCIe efforts began. And now they have joined the UCIe consortium as a contributing member to drive the evolution of the chiplet interface standard.

Alchip Profile and Scorecard

The following slide provides a succinct profile of Alchip. An 81% slice of revenue coming from HPC markets is proof of their dedicated high-performance market focus.

Recently, Alchip announced that its high-performance computing ASIC services are now taking 3nm designs and targeting their first test chip for Q1 2023. The new service targets TSMC’s latest N3E process technology. With this announcement, Alchip becomes the first dedicated high-performance ASIC company to announce total design readiness of their design and production ecosystem for 3nm process. Their press announcement mentioned the other assets in place include a complete library of best-in-class 3rd party IP covering DDR5, GDDR6, HBM2E, HBM3, PCIe5, and 112G SERDES IP from Tier 1 providers.

You can learn more at www.alchip.com. You will find a compendium of Alchip related articles and press releases on SemiWiki here.

Also read:

Alchip Reveals How to Extend Moore’s Law at TSMC OIP Ecosystem Forum

Alchip is Painting a Bright Future for the ASIC Market

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.