Wanna become the double patterning guru at your company? David Abercrombie, DFM Program Manager for Calibre, has written a series of articles detailing the multifaceted impacts of double patterning on advanced node design and verification. For designers struggling to understand the complexity and nuances of double patterning,… Read More

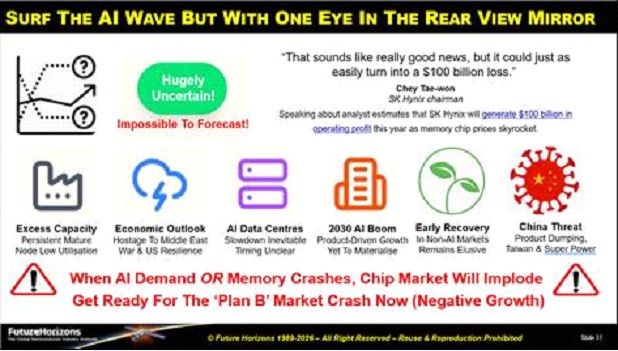

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

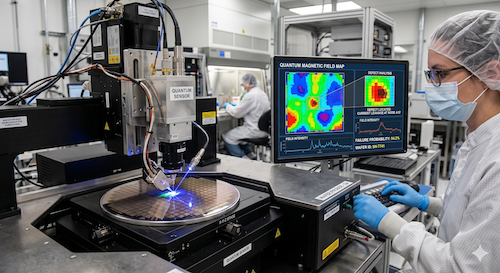

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read MoreSystemC vs C++ for High Level Synthesis

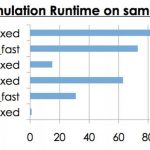

One of the decisions that needs to be made when using high-level synthesis (HLS) in general and Catapult in particular is what language to use as input. The choice is C++ or SystemC. Of course at some level SystemC is C++ with added libraries and templates, but in fact the semantics of the two languages end up being very different.

The… Read More

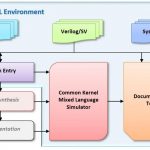

An FPGA Design Flow with Aldec Tools

I’ve used FPGA vendor-supplied tools from both Xilinxand Lattice Semibefore, so I wanted to see what EDA tools Aldec has to offer for FPGA design. I read the Aldecwhite paper, Corporate Standardization of FPGA Design Flow, and summarize what I found.… Read More

Mixed-Signal Methodology Guide: Design Management

I reviewed the book Mixed-Signal Methodology Guidein August of this year published by Cadence, and decided to follow up with one of the authors, Michael Henrie from ClioSoft, to learn more about the importance of Design Management for AMS. Michael is a Software Engineering Manager at ClioSoft and has worked at Zarlink Semi, Legerity,… Read More

Don’t miss this Panel! Platform & Subsystem IP: Trends and Realities

If you pass by Grenoble tomorrow (Tuesday 4th Dec.) and go to IP-SoC 2012, then you should attend this panel at 4pm in the Auditorium (you can’t miss it, it’s the larger room at the registration level).

If you are Designer, Architect, Project Manager, Marketing… working for a chip maker, please prepare questions!… Read More

Arteris answer to Sonics: should compare actual NoC (in Silicon proven SoC) performance, instead of potential, unproven NoC performances!

It seems that Ateris vs. Sonics war, initiated by Sonics in 2010 on the legal battle field, is now continuing on the marketing field, as far as I am concerned, I prefer the latter, as I am an engineer and not a lawyer, and I must say that playing in the marketing allow both companies to extract the most attractive features of their products.… Read More

ST Microelectronics: Strategic Options

ST Microelectronics announced yesterday that it would have a conference call on December 10th to announce its strategy going forward. ST has been struggling the last couple of years, with revenues down year to year. From 2010-2012 (the last an estimate of course) it did $10.3B, $9.6B and $8.4B so it has shrunk nearly 20% in 3 years.… Read More

Variation-Aware Design: A Hands-on Field Guide

IC designers using advanced nodes are acutely aware of how variation effects in the silicon itself are causing increased analysis and design efforts in order to yield chips at acceptable levels. Four authors from Solidoare so passionate about this topic that they combined their years of experience into a book that I had a chance… Read More

Accelera Technical Excellence Award

The Accellera Systems Initiative, most well-known for driving the standardization of various aspects of Verilog and SystemVerilog before handing the standards off to the IEEE, has announced that nominations are open for the 2013 Technical Excellence Award. This recognizes outstanding contributions in the creation of EDA… Read More

Challenges of Implementing LTE

LTE (Long Term Evolution) is the true 4G standard for cellular and, over time, wireless internet. In fact it is several different standards with different levels of performance. LTE will eventually be the only technology used in cellular, voice will simply be Voice-over-IP (VoIP, the same technology that companies like Skype… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior