IC designers using advanced nodes are acutely aware of how variation effects in the silicon itself are causing increased analysis and design efforts in order to yield chips at acceptable levels. Four authors from Solidoare so passionate about this topic that they combined their years of experience into a book that I had a chance… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MoreAccelera Technical Excellence Award

The Accellera Systems Initiative, most well-known for driving the standardization of various aspects of Verilog and SystemVerilog before handing the standards off to the IEEE, has announced that nominations are open for the 2013 Technical Excellence Award. This recognizes outstanding contributions in the creation of EDA… Read More

Challenges of Implementing LTE

LTE (Long Term Evolution) is the true 4G standard for cellular and, over time, wireless internet. In fact it is several different standards with different levels of performance. LTE will eventually be the only technology used in cellular, voice will simply be Voice-over-IP (VoIP, the same technology that companies like Skype… Read More

Sequential Power Optimization

Calypto has an interesting webinar coming up about Minimizing RTL Power Through Sequential Analysis. It is next Tuesday December 4th at 11am.

Insert standard paragraph about how power is the new timing, everyone worries about power, battery life in smartphones, half-empty datacenters.

You probably already know about clock… Read More

8 Reasons Why I Love My iPhone 5

This is a follow up post to 8 Reasons Why I Hate my iPhone 5. The reader’s digest summary is that I started my smartphone journey with Android and became accustomed to the Android way of doing things. It was a difficult jump into the Apple ecosystem. I’d wager that the vast majority of smartphone users stay with their initial platform,… Read More

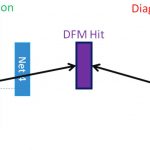

GLOBALFOUNDRIES and Mentor Develop Methods to Identify Critical Features in IC Designs

Since the beginning of the semiconductor industry, improving the rate of yield learning has been a critical factor in the success silicon manufacturing. Each fab has dedicated yield teams that look at the yield of wafers manufactured the previous day and attempt to find the root cause of any unexpected “excursions.” In earlier… Read More

AMS IC Design at Rohde & Schwarz

I met Frank Wiedmann on LinkedIn because we are both members of the Analog Mixed Signal group, and he has an interesting background in AMS IC design.

Since he lives in Munich we conducted our interview by email.… Read More

Give me a pair of wires, I’ll give you Ethernet in cars

A very astute gentleman said to me a few years ago that he’d seen a lot of networking technology come and go – Token Ring, FDDI, Fibre Channel, InfiniBand – but the only one that held up over time was Ethernet.… Read More

Anyone Can Build a Phone

Today’s Dilbert cartoon is about how anybody can build a smart phone. As if it was a technical problem these days. But back in the mid-90s it really was. All the contract manufacturers like Solectron and others figured that since they could build a PC they could build a phone. It turned out that building radios was really hard.… Read More

Will Andy Grove Save Intel By Recruiting Jen Hsun Huang?

Intel may not know it but they are entering a crises moment due to the announced resignation of Paul Otellini that will not take place until May 2013. A six-month funeral with a 100,000 mourning employees will not calm customers who question whether to stick with the x86 PC roadmap much less the Atom mobile processors. A more dramatic… Read More

Solving the EDA tool fragmentation crisis