GLOBALFOUNDRIES will show off its 28nm design ecosystem at #48DAC next week in San Diego. The company will feature a full design ecosystem for its 28nm High-k Metal Gate (HKMG) technology, including silicon-validated flows, process design kits (PDKs), design-for-manufacturing (DFM), and intellectual property (IP) in partnership… Read More

An Illuminating Real Number Modeling Example in Functional VerificationI just read an interesting white paper on…Read More

An Illuminating Real Number Modeling Example in Functional VerificationI just read an interesting white paper on…Read More KLAC - OK Qtr/Guide - Slow Growth - 2025 Leading Edge Offset by China - Mask MashKLA put up an OK Quarter & Guide…Read More

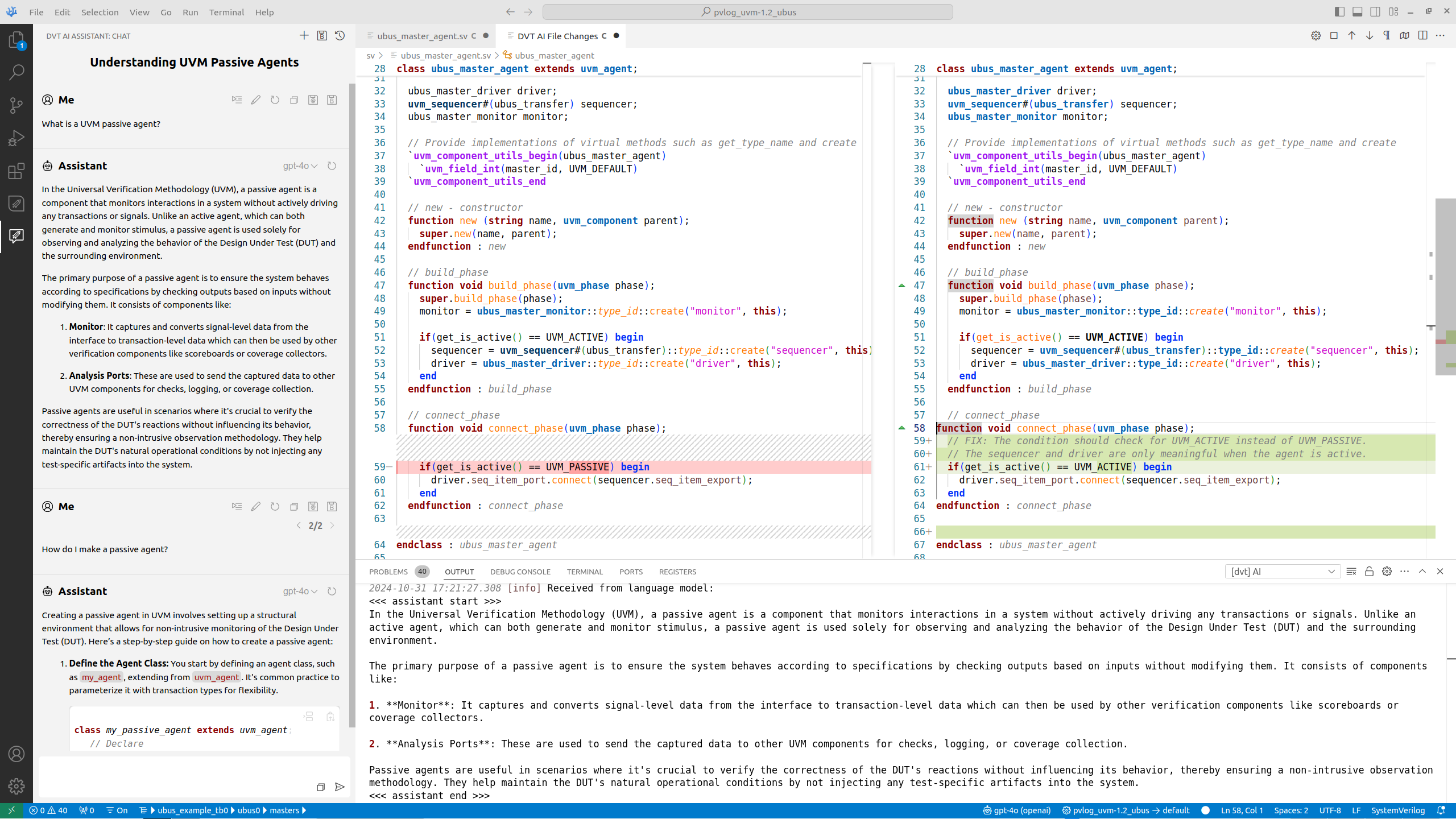

KLAC - OK Qtr/Guide - Slow Growth - 2025 Leading Edge Offset by China - Mask MashKLA put up an OK Quarter & Guide…Read More Adding an AI Assistant to a Hardware Language IDEI’ve been working with AMIQ EDA for several…Read More

Adding an AI Assistant to a Hardware Language IDEI’ve been working with AMIQ EDA for several…Read MoreARM vs Intel step 2…Intel’s nervous breakdown about Microsoft… and cut ATOM price

In the unspoken war between ARM and Intel, a couple of interesting facts have surfaced during the last few days:

- Intel nervous breakdown in respect with their 30 years old accomplice in the Wintel gang

- ATOM latest version Cedar Trail fabbed on 32nm technology, targeted for mobile computing, will be priced at a 30% to 50% discount…

Sagantec 2 Migrate iPad2s @ #48DAC

Sagantec is the leading EDA provider of process migration solutions for custom IC design. Sagantec’s EDA solutions enable IC designers to leverage their investment in existing physical design IP and accomplish dramatic time and effort savings in the implementation of custom, analog, mixed-signal and memory circuits… Read More

Going to DAC? There’s an app for that

Are you going to DAC in San Diego? Do you have an iPhone? In which case Bill Deegan’s dac48 app is something you should install before you get there. It’s free, which makes a nice change from EDA software pricing.

The app substitutes for the various paper, agendas and maps that you need to consult to find exhibitors, check… Read More

New TSMC 28nm Design Ecosystem!

TSMC rolled out the new reference flows for 28nm design as part of the Open Innovation Platform. The biggest surprise (to me) is that Cadence is STILL in the TSMC reference flows!

The updated TSMC OIP wiki is here, the Reference Flow 12.0 wiki can be found here, the AMS 2.0 reference flow wiki is here, and the official TSMC PR is here. … Read More

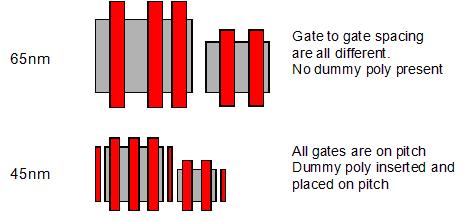

65nm to 45nm SerDes IP Migration Success Story

The problem:To move a single lane variable data rate SerDes (serializer-deserializer) from a 65nm process to a 45nm process, achieving a maximum performance of up to 10.3 Gbps. This is a large piece of complex mixed-signal IP with handcrafted analog circuits. Circuit performance and robustness are critical and must be maintained… Read More

3D IC @ #48DAC

A three-dimensional integrated circuit (3D IC ) is a chip in which two or more layers of active electronic components are integrated both vertically and horizontally into a single circuit. The semiconductor industry is hotly pursuing this emerging technology in many different forms, as a result the full definition is still somewhat… Read More

48th Annual Design Automation Conference

The 48[SUP]th[/SUP] Design Automation Conference (DAC) is now upon us. DAC is billed as “the premier event for the design of electronic circuits and systems, and for EDA and silicon solutions” for which I would have to agree with 100%.

The first DAC I attended was in 1984, Albuquerque New Mexico, which was one of the first to allow … Read More

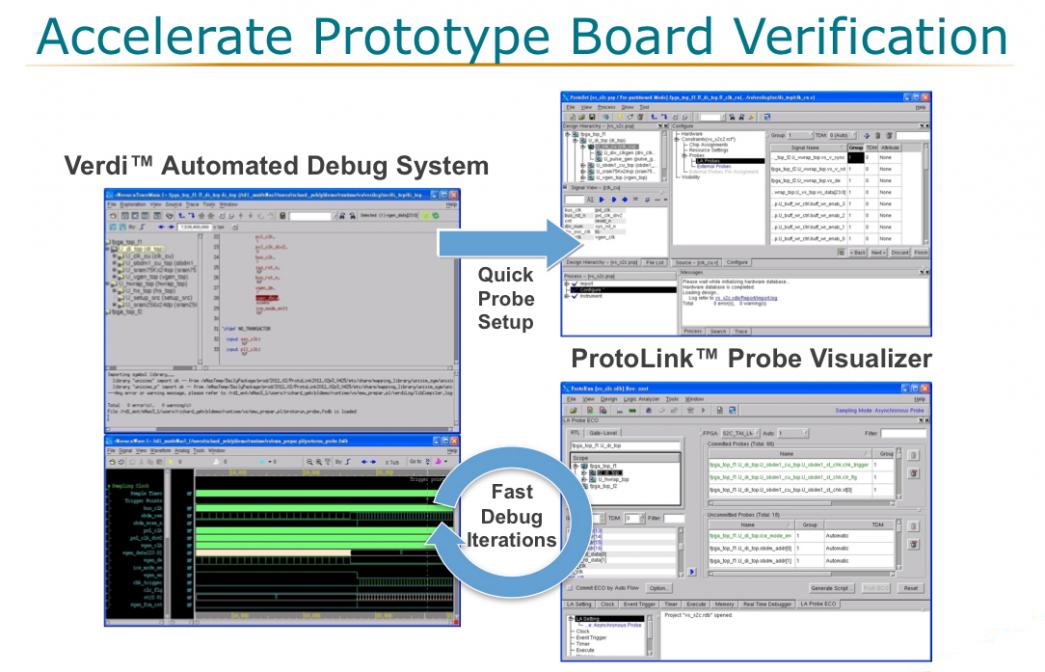

FPGA Prototypes Made Easy

FPGA-based prototype boards are a fast, cost-effective platform for SoC system validation but they are notoriously difficult to set up and to debug. There is a big upside, however, allowing early software integration and testing and thus finding bugs in both the software and the SoC earlier. This approach is much cheaper than … Read More

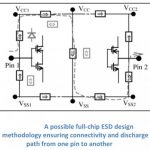

Analyzing and Planning Electro-static Discharge (ESD) Protection

ESD has historically been a big problem analyzed with ad-hoc approaches. As explained earlier, this is no longer an adequate way to plan nor signoff ESD protection.

Pathfinder is the first full-chip comprehensive ESD planning and verification solution. It is targeted to address limitations in today’s methodologies.… Read More

AI Semiconductor Market