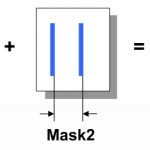

TSMC and Synopsys hosted a webinar in December on this topic of double patterning and how it impacts the IC extraction flow. The 20nm process node has IC layout geometries so closely spaced that the traditional optical-based lithography cannot be used, instead lower layers like Poly and Metal 1 require a new approach of using two… Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read MoreFD-SOI is Worth More Than Two Cores

This is the second blog entry about an ST Ericsson white-paper on multiprocessors in mobile. The first part was here.

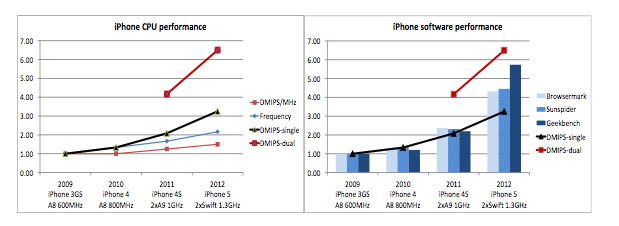

The first part of the white-paper basically shows that for mobile the optimal number of cores is two. It is much better to use process technology (and good EDA) to run the processor at higher frequency rather than add… Read More

Wall Street Does NOT Know Semiconductors!

In my never ending quest to promote the fabless semiconductor ecosystem I cannot pass up a discouraging word about one of the oldest financial services companies. You can consult with me for $300 per hour to answer your questions about the semiconductor industry on the phone or you can buy me lunch and get it in person (lunch will probably… Read More

Mobile SoCs: Two Cores are Better Than Four?

I came across an interesting white-paper from ST Ericsson on two topics: multi-processors in mobile platforms and FD-SOI. FD-SOI is the ST Microelectronics alternative to FinFETs for 20nm and below. It stands for Fully-Depeleted Silicon-on-Insulator. But I’m going to save that part of the white-paper for another blog… Read More

What did CES 2013 mean for #SemiEDA?

CES is the preeminent gadget show, and in the LVCC South Hall a wave has been building for some time. It’s now the place where chipsets are introduced, and this year saw a wide range of introductions from Atmel, Bosch, Broadcom, Intel (OK, they’re still in Central Hall), InvenSense, Marvell, NVIDIA, Qualcomm, Samsung, ST-Ericsson,… Read More

Yawn… New EDA Leader Results Are Coming

We will soon start to see the quarterly financial reporting installments of the “Big 3” public EDA companies. I predict they will be as boring as usual. I am not sure if I would want it any differently though.

Back in the 90s there were times when it was truly interesting to wait to see what Cadence, Mentor, or later Synopsys, might announce.… Read More

Oasys Has a New CEO

Scott Seaton is the new CEO of Oasys Design Systems. Paul van Besouw, the CEO since the company’s founding, becomes the CTO. I met Scott last year when I was doing some consulting work for Carbon Design where he was VP of sales (the new VP sales at Carbon is Hal Conklin, by the way).

I talked to Scott about why he had joined Oasys. … Read More

Buying DDRn Controller IP AND Memory Model to the same IP vendor gives real TTM advantage

We all know the concept of “one stop shop”, becoming popular in the Design IP market. The topic we will address today is NOT the “one stop shop”, even if it looks similar, but rather that we could call “consistent design flow”.

What does that means? Simply that, if your SoC design is integrating a DDRn (LPDDR2, DDR3 or even DDR4, let’s… Read More

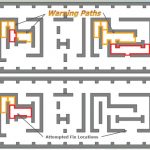

Fixing Double-patterning Errors at 20nm

David Avercrombie of Mentor won the award for the best tutorial at the 2012 TSMC OIP for his presentation, along with Peter Hsu of TSMC, on Finding and Fixing Double Patterning Errors in 20nm. The whole presentation along with the slides is now available online here. The first part of the presentation is an introduction to double … Read More

Mentor @ the TSMC Open Innovation Platform Forum

At TSMC’s Open Innovation Platform (OIP) Ecosystem Forum, Mentor made technical presentations on four different topics, two of them co-presented with TSMC and LSI Corporation. Those presentations are described below with links to downloadable pdf presentation files.

Finding and Fixing Double Patterning Errors in… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!