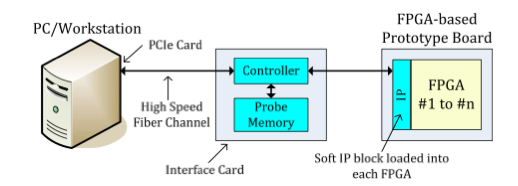

It is no secret that SoC designs continue to increase in complexity and time-to-market windows are shrinking. While there is room for debate on just how big a fraction of SoC design effort goes on verification, there is no debating that it is a large part of the total. Simulation is increasingly too slow, especially when software … Read More

The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More

The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read More

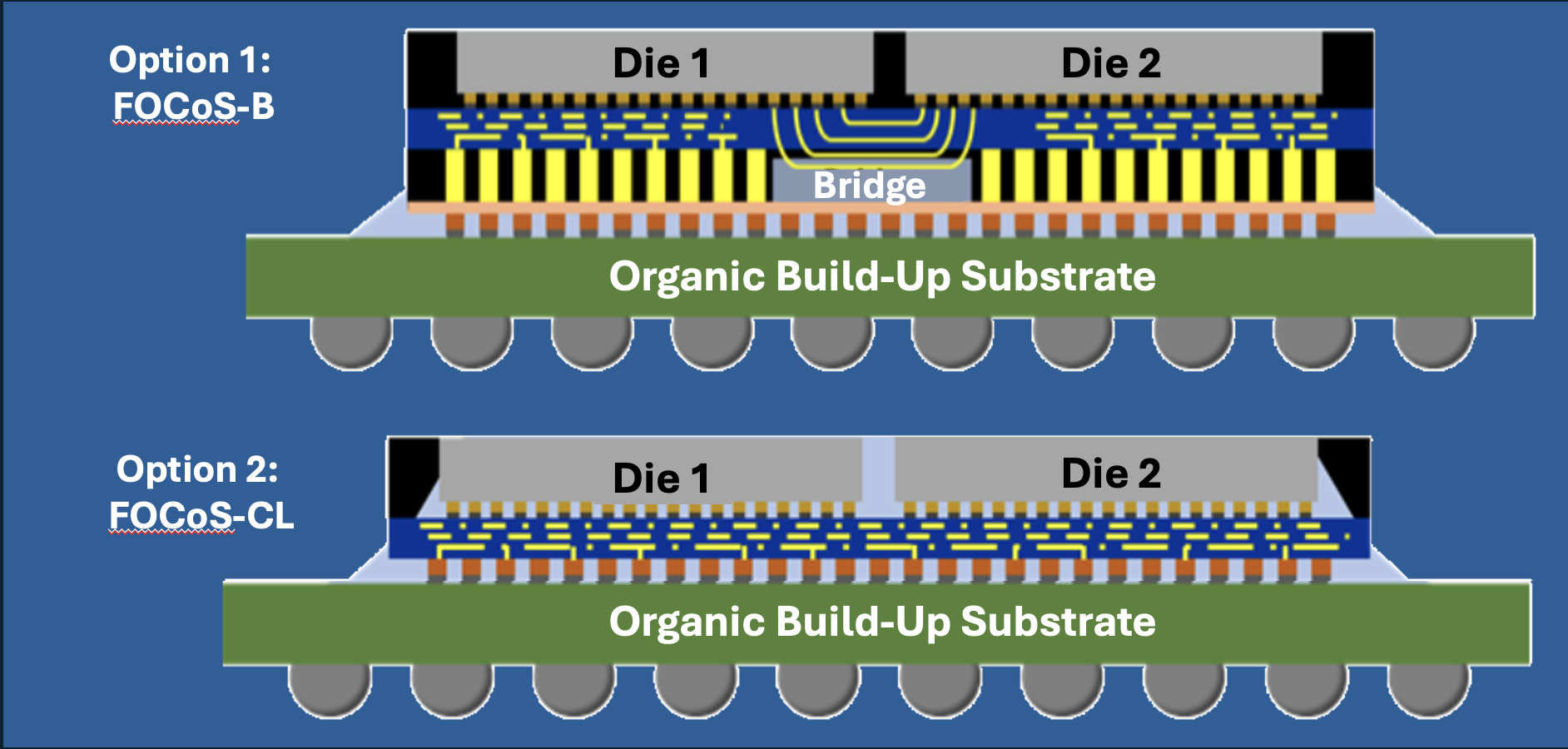

Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read More Addressing Reliability and Safety of Power Modules for Electric VehiclesAs electric vehicles (EVs) gain widespread adoption, safety,…Read More

Addressing Reliability and Safety of Power Modules for Electric VehiclesAs electric vehicles (EVs) gain widespread adoption, safety,…Read More Shaping Tomorrow’s Semiconductor Technology IEDM 2024Anyone who has read my articles about IEDM…Read More

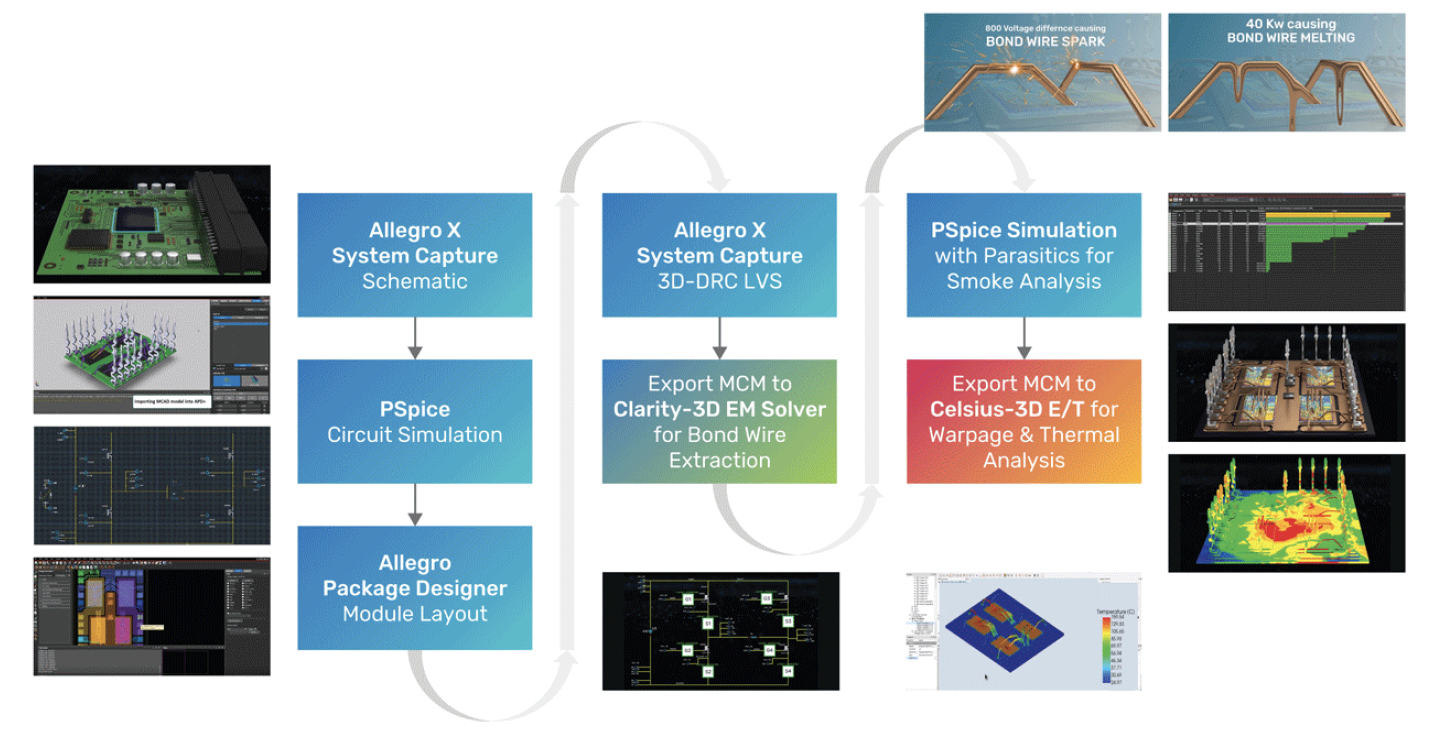

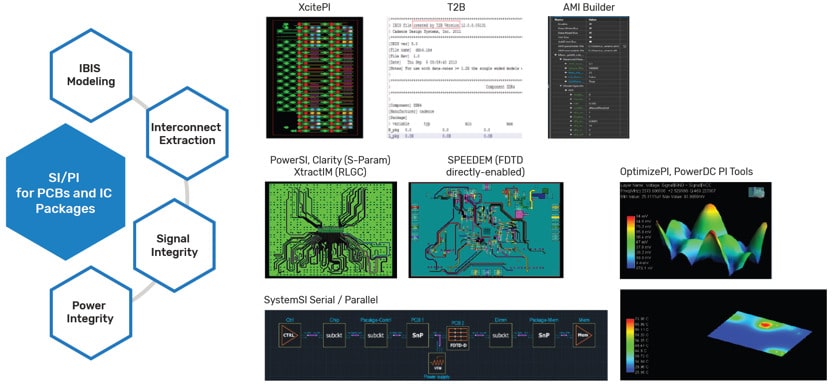

Shaping Tomorrow’s Semiconductor Technology IEDM 2024Anyone who has read my articles about IEDM…Read More SI and PI Update from Cadence on Sigrity XSignal Integrity (SI) and Power Integrity (PI) issues…Read More

SI and PI Update from Cadence on Sigrity XSignal Integrity (SI) and Power Integrity (PI) issues…Read MoreFun Break

At DAC SpringSoft had a couple of video games set up, one about functional verification and one about, surprise, physical layout. But you didn’t need to go to DAC, you can play them now:

Liberate your Layout

Smartphones shipments, Sky is the limit…

…or a global recession, but that’s not the purpose of this blog. As everybody knows, Apple is designing and selling smartphones, only. Does it mean that only smartphones are generating profit in the mobile industry? As we have seen recently in Semiwiki, Apple makes 2/3 of profit of entire mobile industry.

Let’s have a look (below)… Read More

Samsung to Acquire AMD?

Don’t get me wrong, I’m a big fan of AMD, I buy AMD based products whenever possible to prevent an innovation stifling Intel monopoly. Unfortunately Silicon Valley coffee house conversations continue to paint a bleak picture for AMD, even with a recent stock surge on better than expected revenue guidance for the rest of 2011. I’m… Read More

Sentinel-PSI Webinar

The last of the current series of webinars is on Sentinel-PSI,IC-Package, Power and Signal Integrity Solution. It will be at 11am Pacific time on Thursday 11th August. It will be conducted by Dr. Tao Su, product manager of the Sentinel products. Dr. Su has many years of experience in the EDA industry and is specialized in power integrity… Read More

Apple Roadmaps Intel to 14nm

Intel will not win the tablet market with any of the various Atom chips rolling out at 32nm, 22nm and even 14nm. They are too late to a game that Apple owns 90% of today and will so in the future. All of these ultra low power atom versions are like the Saturn test rocket developments that preceded the Apollo 11 Moon Landing. They are necessary… Read More

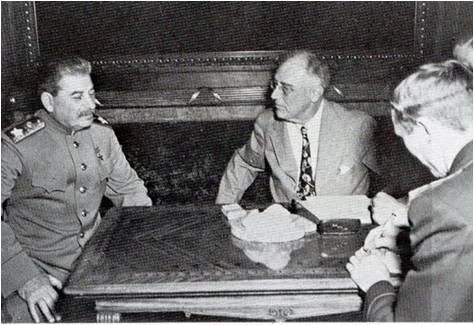

Yalta in EDA: Cadence stronger in VIP territory…

…when Synopsys is getting the lion’s share in Interface IP. In Q2 2010, there was two major acquisitions in EDA world: Synopsys has bought Virage Logic (for more than $300M) when Cadence bought Denali for an equivalent amount. Synopsys bought a 100% IP focused company, when Cadence bought a strongly VIP focused company. Does it … Read More

August 11th – Hands-on Workshop with Calibre: DRC, LVS, DFM, xRC, ERC

I’ve blogged about the Calibre family of IC design tools before:

Smart Fill replaced Dummy Fill Approach in a DFM Flow

DRC Wiki

Graphical DRC vs Text-based DRC

Getting Real time Calibre DRC Results with Custom IC Editing

Transistor-level Electrical Rule Checking

Who Needs a 3D Field Solver for IC Design?

Prevention is Better… Read More

SNUG outside Silicon Valley

SNUG in Silicon Valley was in March so either you were there or you’ve missed it. But it is the summer (and fall) of SNUG in the rest of the world:

SNUG China (in Beijing, Shanghai, Shenzhen) on August 22nd-30th

SNUG Singapore on August 23rd

SNUG Taiwan (in Hsinchu) on August 25-26th

SNUG Japan (in Tokyo) on September 7th

SNUG … Read More

Assertion-based Formal Verification

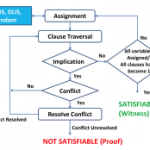

Formal verification has grown in importance as designs have grown and it has become necessary to face up to the theoretical impossibility of using simulation to get complete coverage along with the practical impossibility of simulating enough to even get close.

There are a number of solvers for what is called satisfiability (SAT)… Read More

AI Semiconductor Market