Whether you use a gate-first or gate-last High-k Metal Gate implementation, yield will be your #1 concern at 28nm, which makes variation analysis and verification a big challenge. One of the consulting projects I have been working on with the foundries and top fabless semiconductor companies is High-Sigma Monte Carlo (HSMC) … Read More

Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V SolutionFounded with a vision to create transformative, customizable…Read More

Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V SolutionFounded with a vision to create transformative, customizable…Read More Synopsys-Ansys 2.5D/3D Multi-Die Design Update: Learning from the Early AdoptersThe demand for high-performance computing (HPC), data centers,…Read More

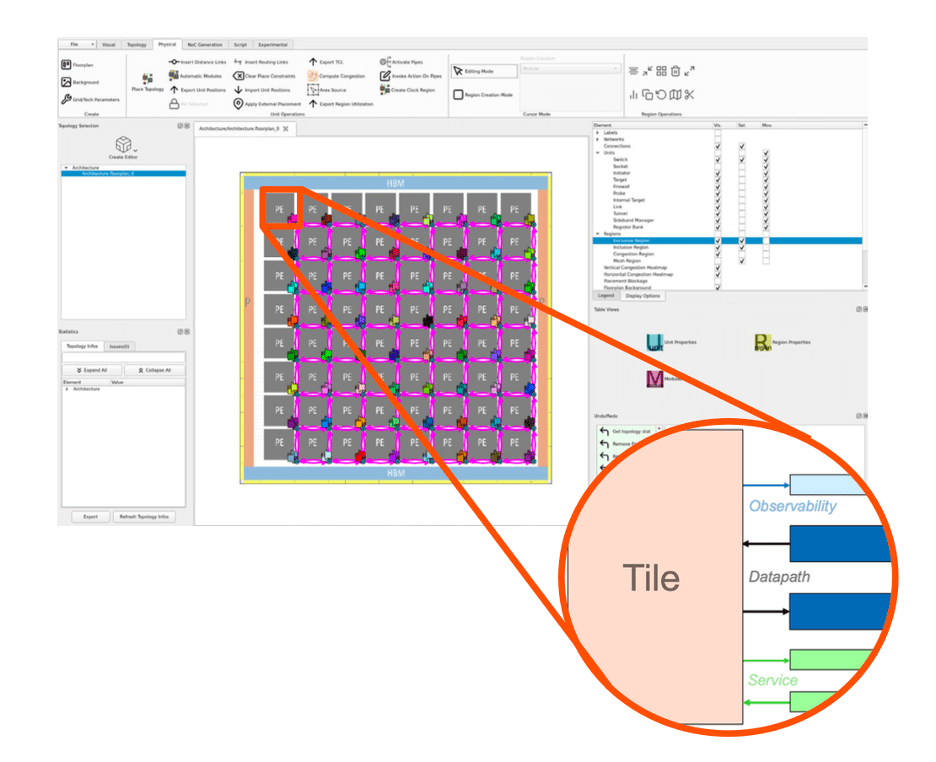

Synopsys-Ansys 2.5D/3D Multi-Die Design Update: Learning from the Early AdoptersThe demand for high-performance computing (HPC), data centers,…Read More Arteris Empowering Advances in Inference AcceleratorsSystolic arrays, with their ability to highly parallelize…Read More

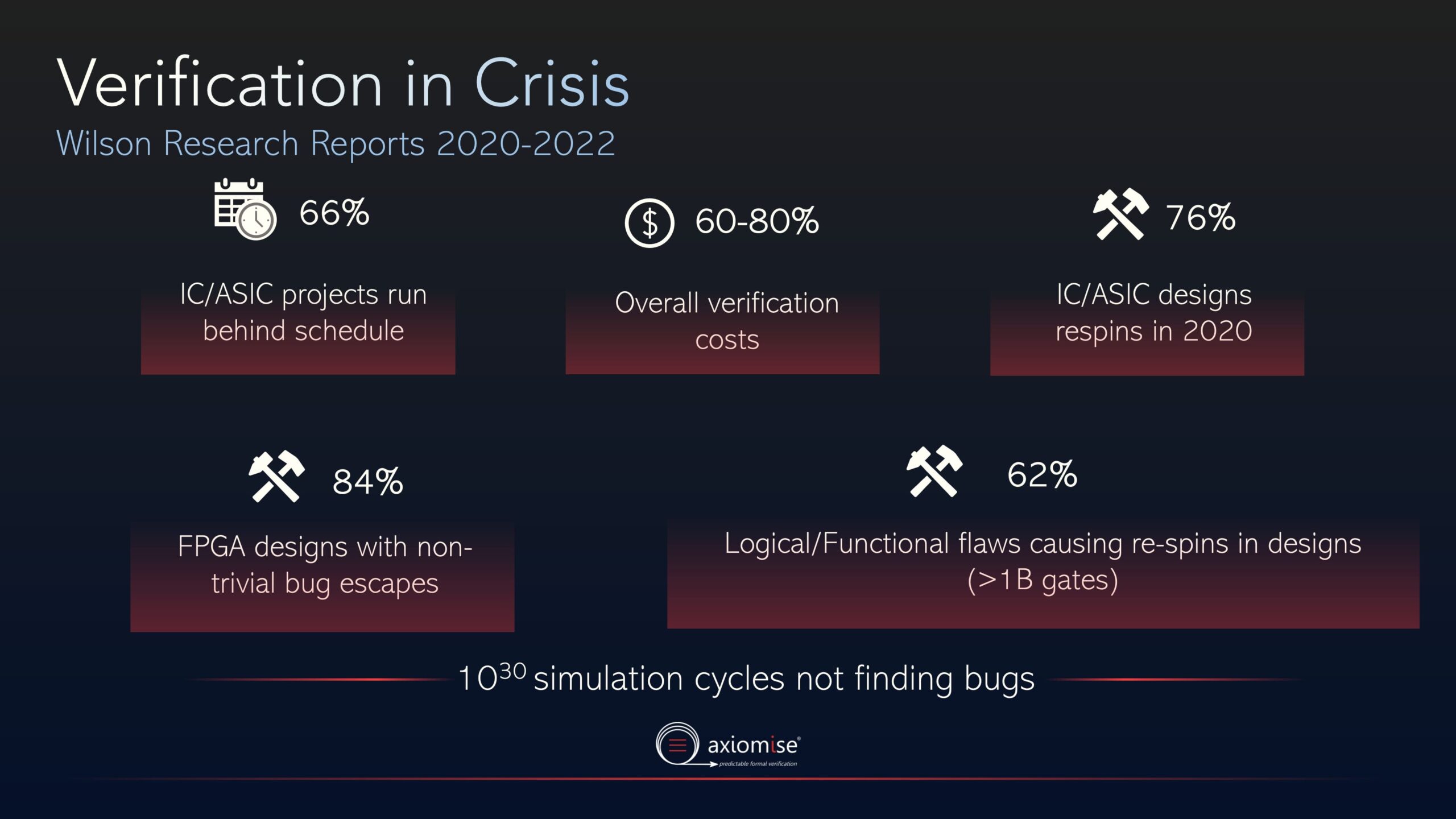

Arteris Empowering Advances in Inference AcceleratorsSystolic arrays, with their ability to highly parallelize…Read More The Convergence of Functional with Safety, Security and PPA VerificationFormal For All! “Do I need a PhD…Read More

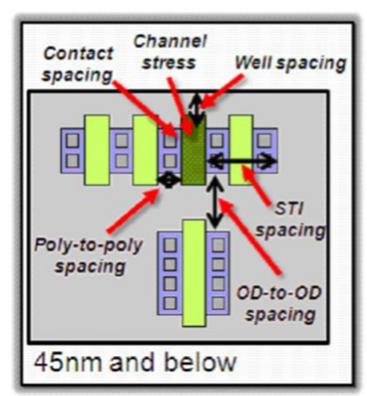

The Convergence of Functional with Safety, Security and PPA VerificationFormal For All! “Do I need a PhD…Read MoreLayout for analog/mixed-signal nanometer ICs

Analog has always been difficult, a bit of a black art persuading a digital process to create well-behaved analog circuits, capacitors, resistors and all the rest. In the distant past, we would solve this by putting the analog on a separate chip, often in a non-leading-edge process. But modern SoCs integrate large amounts of digital… Read More

Will AMD and Samsung Battle Intel and Micron?

We received some good feedback from our article on Intel’s Back to the Future Buy of Micron and I thought I would present another story line that gives readers a better perspective of what may be possibly coming down the road. In this case, it is the story of AMD and Samsung partnering to counter Intel’s platform play with Micron. The… Read More

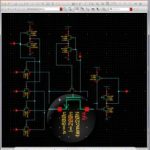

Transistor Level IC Design?

If you are doing transistor-level IC design then you’ve probably come up against questions like:

- What Changed in this schematic sheet?

- How did my IC layout change since last week?

In the old days we would hold up the old and new versions of the schematics or IC layout and try to eye-ball what had changed. Now we have an automated… Read More

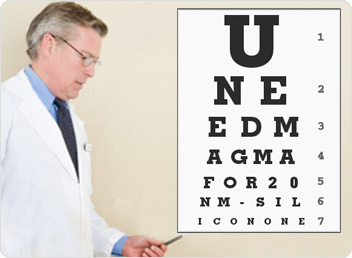

Third Generation DFM Flow: GLOBALFOUNDRIES and Mentor Graphics

Introduction

Mentor Graphics and GLOBALFOUNDRIES have been working together for several generations since the 65nm node on making IC designs yield higher. Michael Buehler-Garcia, director of Calibre Design SolutionsMarketing at Mentor Graphics spoke with me by phone today to explain how they are working with GLOBALFOUNDRIES… Read More

Mentor catapults Calypto

Mentor has transferred its Catapult (high level synthesis) product line, including the people, to Calypto. Terms were not disclosed but apparently it is a non-cash deal. Calypto gets the product line. Mentor gets a big chunk of ownership of Calypto. So maybe the right way to look at this is as a partial acquisition of Calypto.

It … Read More

20nm SoC Design

There are a large number of challenges at 20nm that didn’t exist at 45nm or even 32nm.

The biggest issues are in the lithography area. Until now it has been possible to make a reticle using advanced reticle enhacement technology (RET) decoration and have it print. Amazing when you think that at 45nm we are making 45nm features… Read More

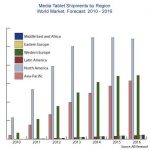

Magic Media Tablet: illusion about a niche market?

According with ABI research, worldwide annual media tablet shipments are expected to top 120 million units in 2015, which is more than decent for a niche market. But if you compare it with the smartphone market (you can find the smartphone shipments forecast here), media tablet will weight 15% in unit shipment of the smartphone … Read More

Itanium Neutron Bombs Hit HP Campuses, Oracle Looking for Survivors

It was a series of Itanium Neutron Bombs detonating during the reign of 4 management teams (Platt, Fiorina, Hurd and Apotheker) that left HP campuses in Cupertino and Palo Alto in the custody of crickets. The devastation to employees and stockholders is absolutely immense and the current strategy calls for a further retreat into… Read More

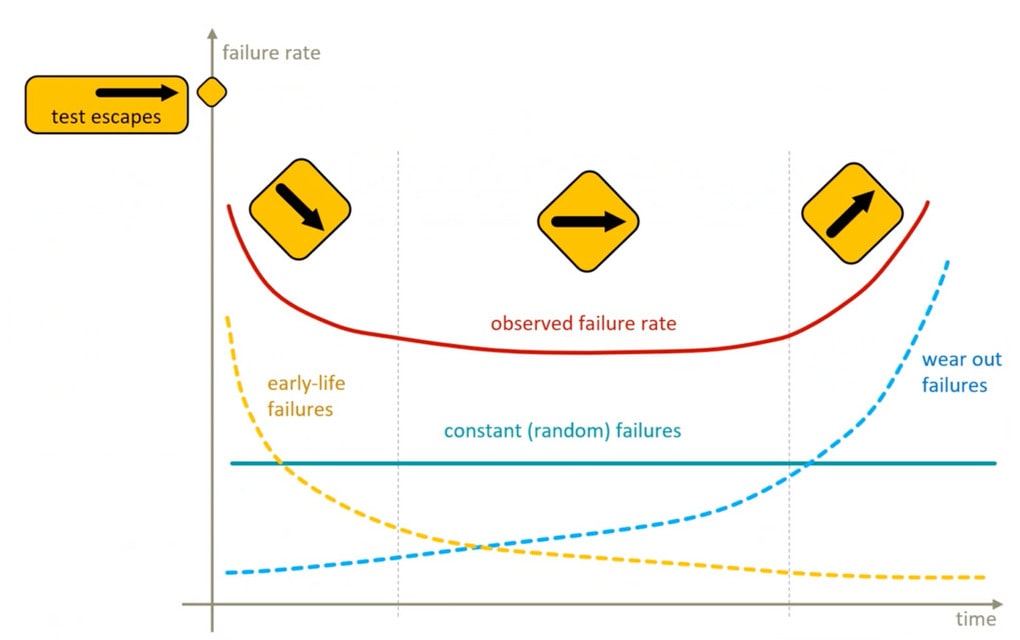

Formal Verification for Post-silicon Debug

OK, let’s face it, when you think of post-silicon debug then formal verification is not the first thing that springs to mind. But once a design has been manufactured, debugging can be very expensive. As then-CEO of MIPS John Bourgoin said at DesignCon 2006, “Finding bugs in model testing is the least expensive and most desired… Read More

Build a 100% Python-based Design environment for Large SoC Designs