As I said yesterday, last week was the GSA Analog/Mixed-Signal working group completely dedicated to FD-SOI. ST went first and had a presentation that was a mixture of an introduction to FD-SOI that I have covered times that are too numerous to mention. Then they did a dive into analog and RF capabilities for FD-SOI that went very … Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreA Security Idea for EDA / Embedded Design

I’m on a mission to find novel ideas for EDA / embedded design tools. One I have been discussing on and off with a DARPA friend for at least a couple of years is how to grade the security of a hardware design or, more comprehensively, the security of an embedded system including hardware and the software running on the hardware.

This feels… Read More

Test Driving Analog/Mixed Signal Design for the Internet of Things

The Internet of Things (IoT) is creating urgent demand for a new generation of analog/mixed-signal (AMS) designs, some of which also contain MEMs. To efficiently create the myriad of AMS devices at the edge of the IoT requires a design environment that is affordable and easy to use, but powerful enough to create the widely diverse… Read More

FD-SOI: Samsung Opens the Kimono a Little

Last week there was a meeting of the GSA Analog/Mixed-Signal (AMS) working group. It was completely focused on FD-SOI (I hate that name, especially since FinFET is also fully-depleted. I vote for BoxFETs.) It was a bases loaded meeting with presentations from ST Microelectronics (calling in from France close to midnight), Samsung… Read More

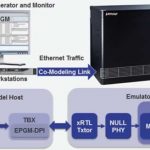

Testing Ethernet with virtual co-modeling

Ethernet is suddenly a hot topic in SoC design again. The biggest news may be this: it’s not just the cloud and enterprise networks. Those are still important applications. The cloud is driving hard for more ports at 25G server and 100G switch speeds according to a recent Dell’Oro Group report. Enterprise networks are driving for… Read More

NIWeek: Xilinx Inside

Being from Britain, NI always means Northern Ireland when I see it. After all the official name of my country is the United Kingdom of Great Britain and Northern Ireland, giving us the same problem as the United States of America, the full name is a mouthful. So we abbreviate the country to UK and call ourselves British or even Brits.… Read More

My Experience with the Ultra Thin 2015 MacBook

Before we left for our 5 week trip to Europe I decided that I would need a real laptop computer on the road. I knew it would be a near necessity for booking hotels and making train reservations. Also, I would need to write emails and maybe even pay some online bills. I already have an iPad but really wanted to be able to run all my applications… Read More

A Complete Simulation Platform for Mobile Systems

If we take an insight into the semiconductor industry, we can easily find that mobile systems are the main drivers of this industry. The Smartphone business has remained at the top since a good number of years. Although the Smartphone sales growth has started showing a sign of stagnation, it is still a main contributor with a solid… Read More

A Paradigm Shift in Microelectronic System Design

A Paradigm Shift

The word “paradigm” is defined in the dictionary as “a framework containing the basic assumptions, ways of thinking, and methodology that are commonly accepted by members of a scientific community”. In his influential book “The Structure of Scientific Revolutions” published in 1962, Thomas Kuhn uses the term… Read More

Four Things a New Semiconductor Technology Must Have to be Disruptive

This post discusses attributes of gallium nitride (#GaN) that make it a disruptive technology and identifies the four factors required for GaN technology to displace silicon as the technology of choice.

Displacing the Silicon with GaN

38 years ago, when I first entered the semiconductor business as a freshly minted Stanford … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era