Earlier this month during my conversation with Dr. Walden C. Rhines, he emphasised the need for our next generation designers to think at system level and design everything keeping the system’s view in mind. The verification will go through major transformation at the system level. I can see the FPGA prototyping systems already… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read MoreThe EDAC Wally Rhines Roast (video)

Last week was the EDAC Phil Kaufman award dinner. It was much more like a roast, probably because Wally has a great sense of humor and as Aart de Geus said, “Wally is a cool cat to have a beer with…” Aart is right of course, hanging with Wally is one of my favorite work things to do.

The place was lousy with media people so I will try and add some… Read More

Maybe Clockless Chip Design’s Time has Come

There have always been novel technologies vying to compete with conventional design practices. It is hit or miss on the success of these ideas. In the 90’s I recall speaking to someone who was convinced that they could effectively build computers based on multilevel logic. This, as we know did not pan out. But there have been many … Read More

More than just mobile phones for Mali

ARM TechCon 2015 was another tour de force for ARM and its ecosystem. Besides some of the developments in mobile, IoT, and security (more coming soon in the Epilogue of “Mobile Unleashed”), there were two topics that I found very educational and will cover in blogs this week. One was how the Mali family is powering more than just mobile… Read More

A (R)evolution in Hardware-based Simulation Acceleration

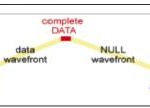

The most exciting products in our industry are those that are both evolutionary and revolutionary. Cadence has just announced an update to their hardware simulation acceleration platform – Palladium Z1 – which continues the evolution of the unique capabilities of processor-based acceleration, plus a revolutionary approach… Read More

Strengthening That Serving ARM

Everyone is aware of ARM’s dominance in mobile devices and their likely dominance in IoT, but what about servers? ARM has been making a play for this area but conventional wisdom is that fortress Intel will protect its server market at all costs. You’ll hear that servers are not so much about compute power, they’re more about I/O and… Read More

ARM Announces Cortex-A35, mbed OS 3.0 at ARM TechCon 2015

Mike Muller, Chief Technology Officer of ARM, has announced the availability of Cortex-A35 processor core for low- to mid-range smartphones at the opening keynote of ARM TechCon on November 10, 2015 in Santa Clara, California. According to Muller, there are going to be 2.8 billion smartphones shipped this year, and more than … Read More

The Reason ARM Will Win IoT!

After spending the week in Silicon Valley at ARM TechCon and related meetings, there was one common thread amongst the presentations and conversations and that was security. No matter what the topic was, mobile, consumer or industrial IoT, wearables, automotive, etc… security always came up. The question I had was how will companies… Read More

When Talking About IoT, Don’t Forget Memory

Memory is a big enough topic that it has its own conference, Memcon, which recently took place in October. While I was there covering the event for SemiWiki.com I went to the TSMC talk on memory technologies for the IoT market. Tom Quan, Director of the Open Innovation Platform (OIP) at TSMC was giving the talk. IoT definitely has special… Read More

A Novel Microprocessor Fighting Dark Silicon, Energy Efficiency, Code density and Silicon area

Processor cores used in computers and smartphones have become impaired by their own complexity and can’t fully utilize future CMOS generations for increasing their efficiency. Due to the continued increase of density and speed of transistors, these big cores produce too much heat per mm[SUP]2[/SUP] if trying to follow Moore’s… Read More

Solving the EDA tool fragmentation crisis