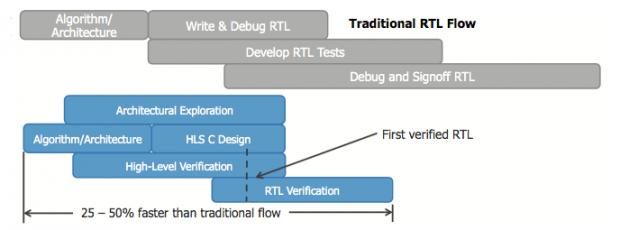

No-one could accuse Badru Agarwala, GM of the Mentor/Siemens Calypto Division, of being tentative about high-level synthesis. (HLS). Then again, he and a few others around the industry have been selling this story for quite a while, apparently to a small and not always attentive audience. But times seem to be changing. I’ve written… Read More

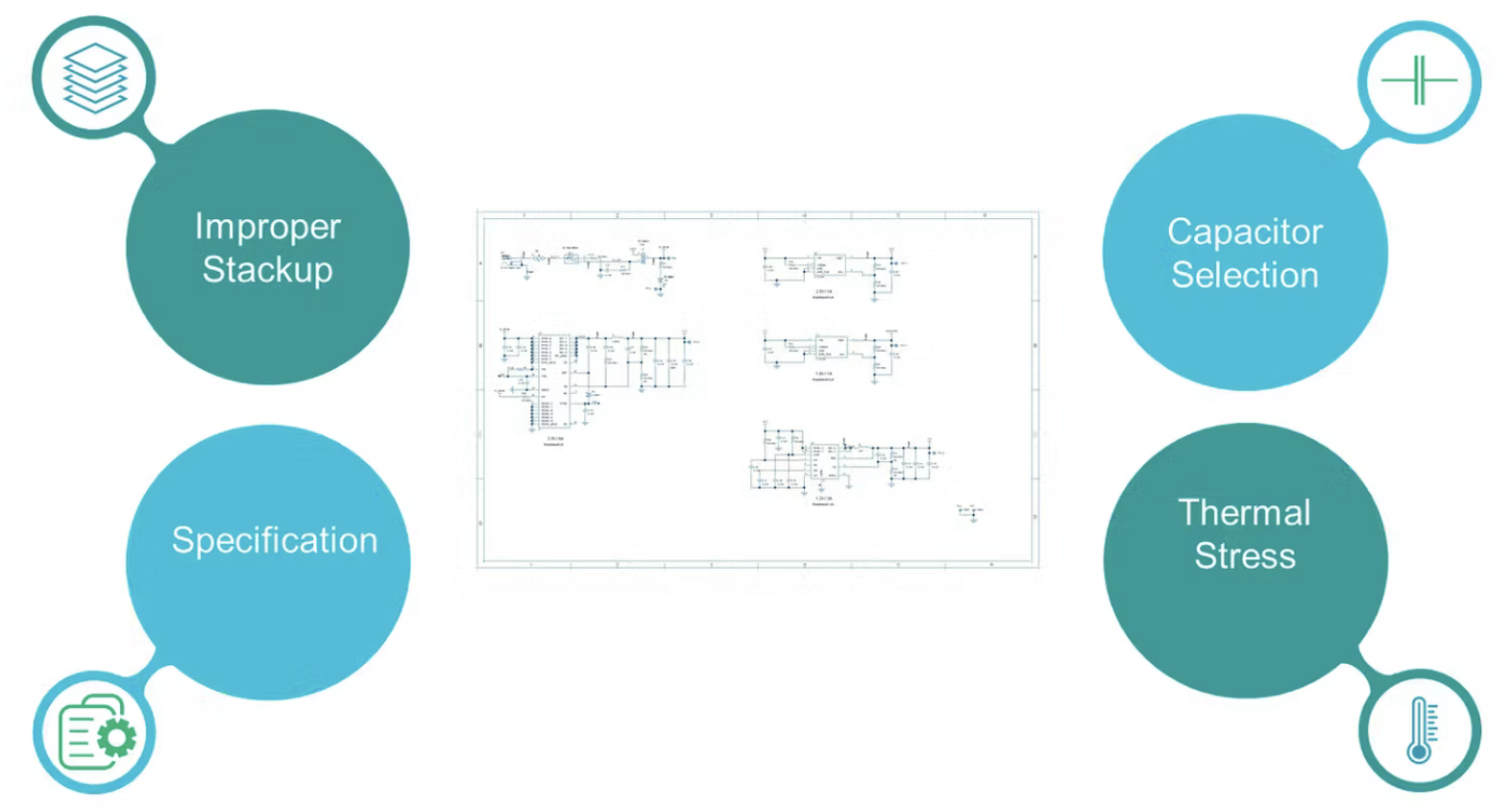

Exploring the Hidden Complexity of Modern Power Electronics Design – A Siemens White PaperReview the specifications of any state-of-the-art microcontroller and…Read More

Exploring the Hidden Complexity of Modern Power Electronics Design – A Siemens White PaperReview the specifications of any state-of-the-art microcontroller and…Read More Renesas Scalable Automotive SoC Design Using Arteris NoCThe increasing complexity of advanced driver assistance systems…Read More

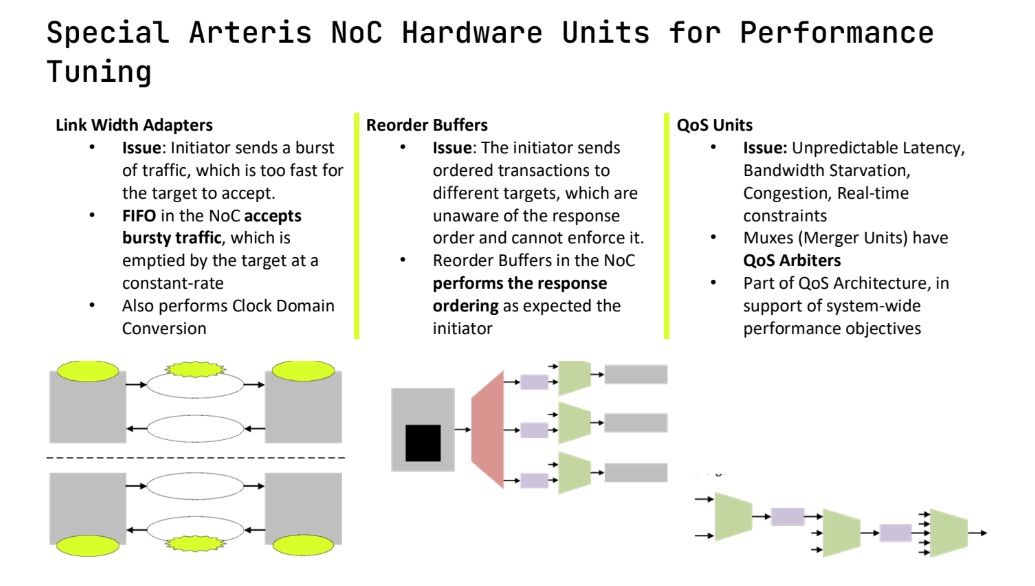

Renesas Scalable Automotive SoC Design Using Arteris NoCThe increasing complexity of advanced driver assistance systems…Read More Calibrating Quantum Computing Activity in Financial ServicesI was invited to listen in on an…Read More

Calibrating Quantum Computing Activity in Financial ServicesI was invited to listen in on an…Read More NoC Matters: Designing the Backbone of Next-Gen AI SoCsModern SoC design for artificial intelligence workloads has…Read More

NoC Matters: Designing the Backbone of Next-Gen AI SoCsModern SoC design for artificial intelligence workloads has…Read MoreChina is right: The world doesn’t need Silicon Valley

Ever since the Chinese Government banned Facebook in 2009, Mark Zuckerberg has been making annual trips there attempting to persuade its leaders to let his company back in. He learned Mandarin and jogged through the smog-filled streets of Beijing to show how much he loved the country. Facebook even created new tools to allow China… Read More

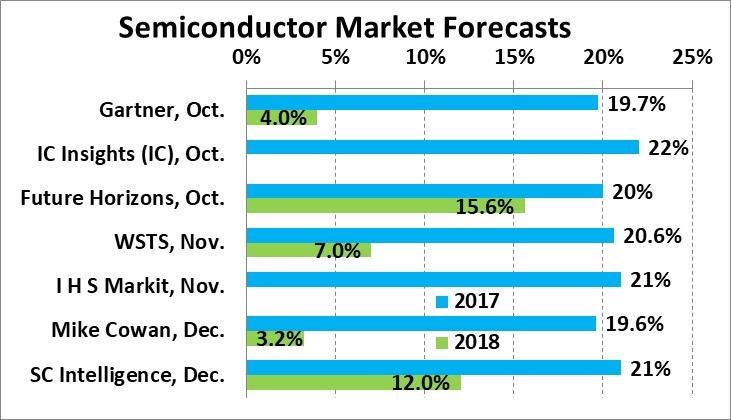

2017 Semiconductors +20%, 2018 slower

The global semiconductor market in 2017 will finish with annual growth of about 20%. Recent forecasts range from 19.6% to 22%. World Semiconductor Trades Statistics (WSTS) data is finalized through October, thus the final year results will almost certainly be within this range. We at Semiconductor Intelligence have raised … Read More

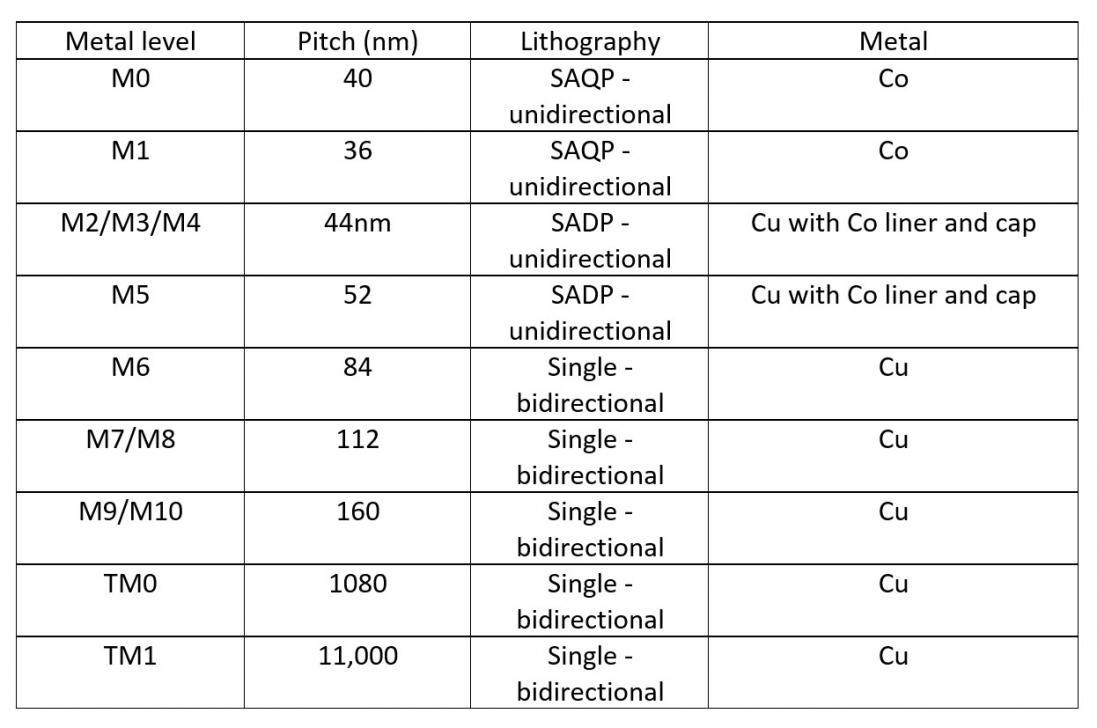

IEDM 2017 – Intel Versus GLOBALFOUNDRIES at the Leading Edge

As I have discussed in previous blogs, IEDM is one of the premier conferences to learn about the latest developments in semiconductor technology. … Read More

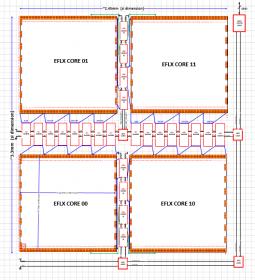

"The Year of the eFPGA" 2017 Recap

This past January, I had postulated that 2017 would be the “Year of the Embedded FPGA”, as a compelling IP offering for many SoC designs (link). As the year draws to a close, I thought it would be interesting to see how that prediction turned out.

The criteria that would be appropriate metrics include: increasing capital investment;… Read More

Embedded In-chip Monitoring, Webinar Recap

Six years ago I first interviewed Stephen Crosher, CEO and Co-founder of Moortecas they were in startup mode with some new semiconductor IP for temperature sensing, and earlier this month I attended their webinar all about embedded in-chip monitoring to get caught up with their technology and growing success. Ramsay Allen is … Read More

Aldec and High-Performance Computing

Aldec continues to claim a bigger seat at the table, most recently in their attendance at SC17, the supercomputing conference hosted last month in Denver. I’m really not sure how to categorize Aldec now. EDA company seems to miss the mark by a wide margin. Prototyping company? Perhaps, though they have a much stronger focus on end-applications… Read More

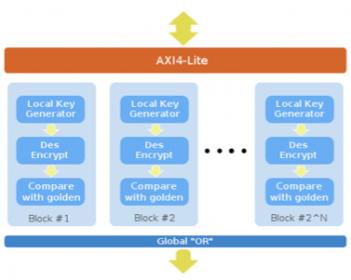

Test Compression for Mission Critical SoCs

With the advent of the Internet-of-Things (IoT), Industry 4.0, Cognitive Computing, and autonomous vehicles and robots we are seeing an unprecedented number of systems-on-a-chip (SoCs) going into mission-critical applications. To accomplish the complexity of these applications, SoCs are being manufactured in leading-edge… Read More

Going to CES 2018? Don’t Miss CEVA-powered Demos!

CES 2018 will start soon and will be held on January 9-12 in Las Vegas. If you plan to go to Vegas, don’t miss CEVA-powered smart and connected products and demos! CEVA’s product portfolio includes DSP IP cores (the smart) and RivieraWaves IP platforms supporting wireless protocols, like WiFi and Bluetooth (the connected).

DSP … Read More

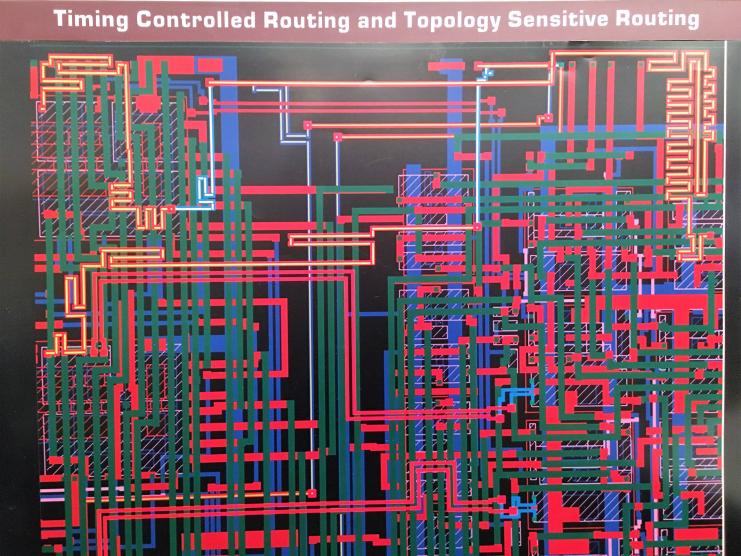

Is there anything in VLSI layout other than “pushing polygons”? (4)

The year is now 1991 and in search for a more peaceful life we decided to move to Canada. At that time, very few companies had advanced flows in VLSI but Ottawa having BNR, Northern Telecom, Mitel, etc., looked to be the most promising place. After a few hiccups in finding a job, I landed in MOSAID, a small company with35 people at that … Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute Blueprint