“Testing can only prove the presence of bugs, not their absence,” stated the famous computer scientist Edsger Dijkstra. That notion rings true to the many college participants of the Hack@DAC competition offered during DAC 2018 in San Francisco. The goal of this competition is to develop tools and methods for identifying security… Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read MoreWebinar: Differential Energy Analysis for Improved Performance/Watt in Mobile GPU

May want to listen up; Qualcomm are going to be sharing how they do this. There is a constant battle in designing for low power; you don’t accurately know what the power consumption is going to be until you build it, but by the time you’ve built it, it’s too late to change the design. So you have to find methods to estimate power early on,… Read More

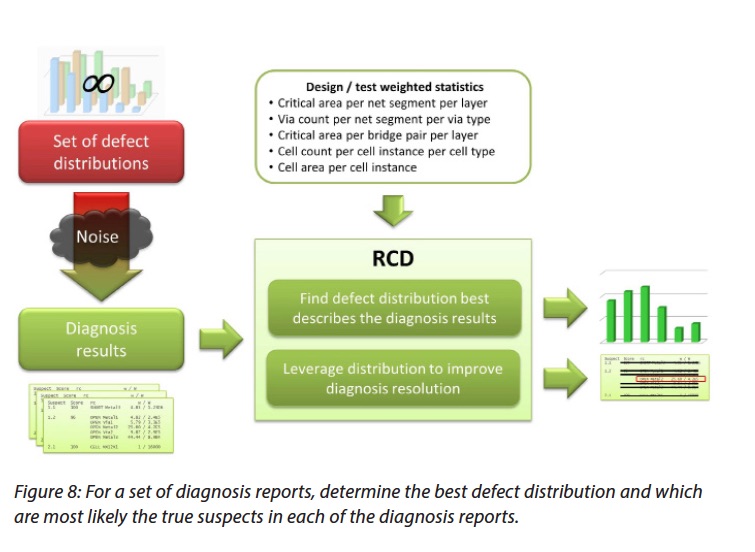

Machine Learning Meets Scan Diagnosis for Improved Yield Analysis

Naturally, chips that fail test are a curse, however with the advent of Scan Logic Diagnosis these failures can become a blessing in disguise. Through this technique information gleaned from multiple tester runs can help pin down the locations of defects. Initially tools that did Scan Logic Diagnosis relied on the netlist to filter… Read More

Deep learning fueling the AI revolution with Interlaken IP Subsystem

AI is revolutionizing and transforming virtually every industry in the digital world. Advances in computing power and deep learning have enabled AI to reach a tipping point toward major disruption and rapid advancement. However, these applications require much higher performance and bandwidth requiring new kinds of IP and… Read More

Samsung Memory is easy come easy go but for how low?

Lam Research (LRCX) reported a great June quarter coming in at $3.126B in revenues and $5.31 in EPS easily beating the street’s $3.06B and EPS of $4.94. However no one will care as guidance for the September quarter is for $2.3B in revs and EPS of $3.20, way, well below the already downward revised estimates of $2.77B and $3.88.… Read More

Daniel’s #55DAC Trip Report

Another year, another DAC, and last month it was #55DAC in SFO and the first thing that I noticed was that the event was no longer located in the traditional North or South Halls, rather we were in the smaller, Moscone West on two floors, almost like a 3D FinFET. Checkin to get my badge was highly automated and oh so fast, well done.… Read More

1-on-1 with Anirudh Devgan, President, Cadence

At the Design Automation Conference, no one is busier than an EDA company executive — conference panels, product launch briefings, customer meetings, and corporate dinners all place considerable demands on their time. I was fortunate enough to be able to meet with Anirudh Devgan, President of Cadence, at the recent DAC55 in San… Read More

Stubbornness Captures an Entire Disruptive Technology and Leads to an Academy Award

This is the eighth in the series of “20 Questions with Wally Rhines”

In 1972, I joined TI and was assigned to work on a new contract that had just been awarded and badly needed staffing. The U.S. Department of Defense had decided that solid-state charge-coupled device (CCD) image sensors were going to be a strategic technology… Read More

Low Cost Power NB-IoT Solution? Fusion F1 DSP based Modem!

Supporting NB-IoT requires low cost (optimized silicon footprint) and ultra-low power solution to cope with IoT device requirement. Cadence Fusion F1 DSP IP has been integrated in modem IC by two new customers, Xinyi and Rafael, gaining traction in NB-IoT market. These design-win builds on previous momentum: software GPS solution… Read More

Cadence Selected to Support Major DARPA Program

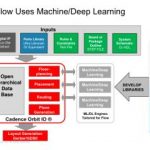

When DARPA plans programs, they’re known for going big – really big. Which is what they are doing again with their Electronics Resurgence Initiative (ERI). Abstracting from their intro, this is a program “to ensure far-reaching improvements in electronics performance well beyond the limits of traditional scaling”. This isn’t… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center