You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

On Star Trek when they asked the computer to do something, they never heard it say “Sorry, you have no photon torpedoes connected to your account”. However, this sort of thing is something that happens at my house when I forget the exact name of a specific light. How did I get here?

I was reluctant to buy a “home assistant” for all the reasons… Read More

It should come as no big surprise that Samsung will miss its Q4 numbers. The company pre announced that profits will be 10.8T KWON (about $9.7B ) versus the 13.2T KWON analysts had predicted, close to a 20% miss. This number is also down about 39% sequentially. Revenue at 59T KWON instead of expected 62.8T KWON and down about 10%. The… Read More

The often pedantic debate over how cars will directly communicate with other cars and infrastructure will culminate suitably at CES 2019 with multiple C-V2X announcements and demonstrations. Foremost among those demonstrations will be parking lot drive-arounds at the Rio Resort Hotel put on by Ford Motor Company, Audi of America… Read More

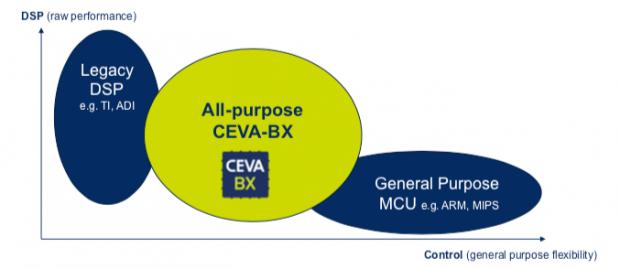

I’ve noticed hybrid solutions popping up recently (I’m reminded of NXP’s crossover MCU released in 2017). These are generally a fairly clear indicator that market needs are shifting; what once could be solved with an application processor or controller or DSP or whatever, now needs two (or more) of these. In performance/power/price-sensitive… Read More

After the onslaught of IoT devices Christmas brought to the masses we really need to talk about security or lack thereof. Do me a favor and count how many IoT devices you have now? Our house IoT count is probably a bit higher than average due to my technology addiction but we are firmly in the double digits and the security breach stories… Read More

While writing the definitive book on ARM history we could not have imagined a more different exit than the SoftBank acquisition, not even close. It is now very clear why SoftBank acquired ARM for $31B. It is also very clear why alternatives like RISC-V are trending on SemiWiki and will continue to do so, absolutely. No matter what … Read More

When Nvidia changed its automotive market messaging from an infotainment-centered theme to autonomous driving two years ago – pronouncing the coming tidal wave of robotaxi development – it matched the almost identical epiphany reached by Intel years prior. Automotive infotainment is a low volume, low revenue… Read More

The annual trek to Las Vegas arrives this year with visions of sinusitis, chapped lips, flat feet and new concepts for automotive cockpit systems. It is no coincidence that the plaza in front of the Las Vegas Convention Center is dominated by automotive exhibits – along with multiple automated driving demonstrations across the… Read More

Attendees of CES 2019 arriving at Las Vegas McCarran International Airport next week will have four options for getting to their hotels: a shuttle offering two rides for the price of one (out and back for about $15); a taxi offering one ride for the price of two (about $30), a Lyft or Uber offering one ride for the price of one ride (about… Read More

Strong Overall Market Growth but a Slowdown Looms

After six years of single digit percentage growth in the overall semiconductor market, 2017 saw almost 22% growth and 2018 year-to-date is up roughly 17% (based on numbers published by the world semiconductor trade statistics). The big growth driver the last two years has been … Read More

Is Intel About to Take Flight?