When PSS comes up, a lot of mainstream verification engineers are apt to get nervous. They worry that just as they’re starting to get the hang of UVM, the ivory tower types are changing the rules of dynamic verification again and that they’ll have to reboot all that hard-won UVM learning to a new language. The PSS community and tool … Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

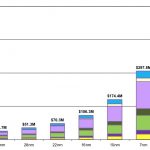

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreUber Lyft and the Price of Greed

Uber and Lyft blew it with their initial public offerings over the past couple weeks. Both companies opted to cash out founders and early investors while tossing pennies to long-supportive drivers in the form of bonuses. The short-term cash out focus could sound the death knell of these market leaders.

Both companies extracted… Read More

Learning on the Edge Investment Thesis

It is said that it will cost as much as $600M to develop a 5nm chip. At that price, only a few companies can afford to play, and with that amount of cash in, innovation is severely limited.

At the same time, there is a stampede in the artificial intelligence (AI) market where around 60 startups have appeared, many of which have already … Read More

Chips are the bleeding edge of China trade war Recovery

Last week we warned of a further down leg due to China trade. We were surprised how quickly our prediction came true as it appears we are now in the midst of giving back all the upside built in to stocks based on a peaceful resolution of the trade conflict which obviously isn’t happening.

Many of the semi stocks we cover were down… Read More

IC to Systems Era

One of my favorite EDA disruptions is the Siemens acquisition of Mentor, pure genius. Joe Sawicki now runs the Mentor IC EDA business for Siemens so we will be seeing him at more conferences and events than ever before. Joe did a very nice keynote at the recent U2U conference that I would like to talk about before we head to the 56thDAC… Read More

The IoT will meet 5G soon, but not with the old SIM cards

By now you have probably realized that 5G is a lot more than an incremental change from previous 3G and 4G cellular technology. For instance, 5G will be used to connect our phones in completely new ways, such as with microcells in urban areas using mm-wavelength signals. 5G will also include two low power protocols that are intended… Read More

56thDAC ClioSoft Excitement

As the number one 56thDAC supporting portal we will publish what’s happening in the conference, on the exhibit floor, and outside activities. The SemiWiki bloggers will be out in full force with live coverage and behind the scenes looks. Remember, SemiWiki bloggers are actual semiconductor professionals with hundreds… Read More

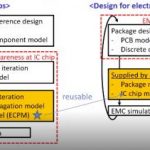

Getting to EMC Compliance by Design

At the risk of highlighting my abundant lack of expertise in the domain, I had always viewed EMC (electromagnetic compatibility) compliance and testing as one of those back-end exercises that can only be done on the real device and depends on a combination of expertise and brute-force in chip/package/module/system design (decaps,… Read More

Achieving a Predictable SignOff in 7nm

Designing with advanced-nodes FinFETs such as 7nm node involves a more complex process than prior nodes. As secondary physical effects are no longer negligible, the traditional margin-based approach applied at various design abstraction levels is considered ineffective. Coupled with the increase of device counts, failing… Read More

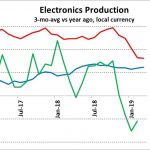

Trade war shifts electronics production

The U.S. is showing steady growth in electronics production. Three-month-average change versus a year ago (3/12) in March 2019 was 6.2%, the 12[SUP]th[/SUP] consecutive month of growth above 5%. China electronics production is decelerating, with March 2019 3/12 growth of 8.2%, similar to 8.3% in February. This marks the first… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center