Cadence recently held an event to dig into the emerging world of photonic computing. Called The Rise of Photonic Computing, it was a two-day event held in San Jose on February 7th and 8th. The first day of the event was also accessible virtually. I attended a panel discussion on the topic – more to come on that. The day delivered a rich… Read More

Collaboration Required to Maximize ASIC Chiplet ValueIt is a well-known fact that chiplets provide…Read More

Collaboration Required to Maximize ASIC Chiplet ValueIt is a well-known fact that chiplets provide…Read More Andes Technology is Expanding RISC-V’s Horizons in High-Performance Computing ApplicationsBy: Dr. Charlie Su, President and CTO, Andes…Read More

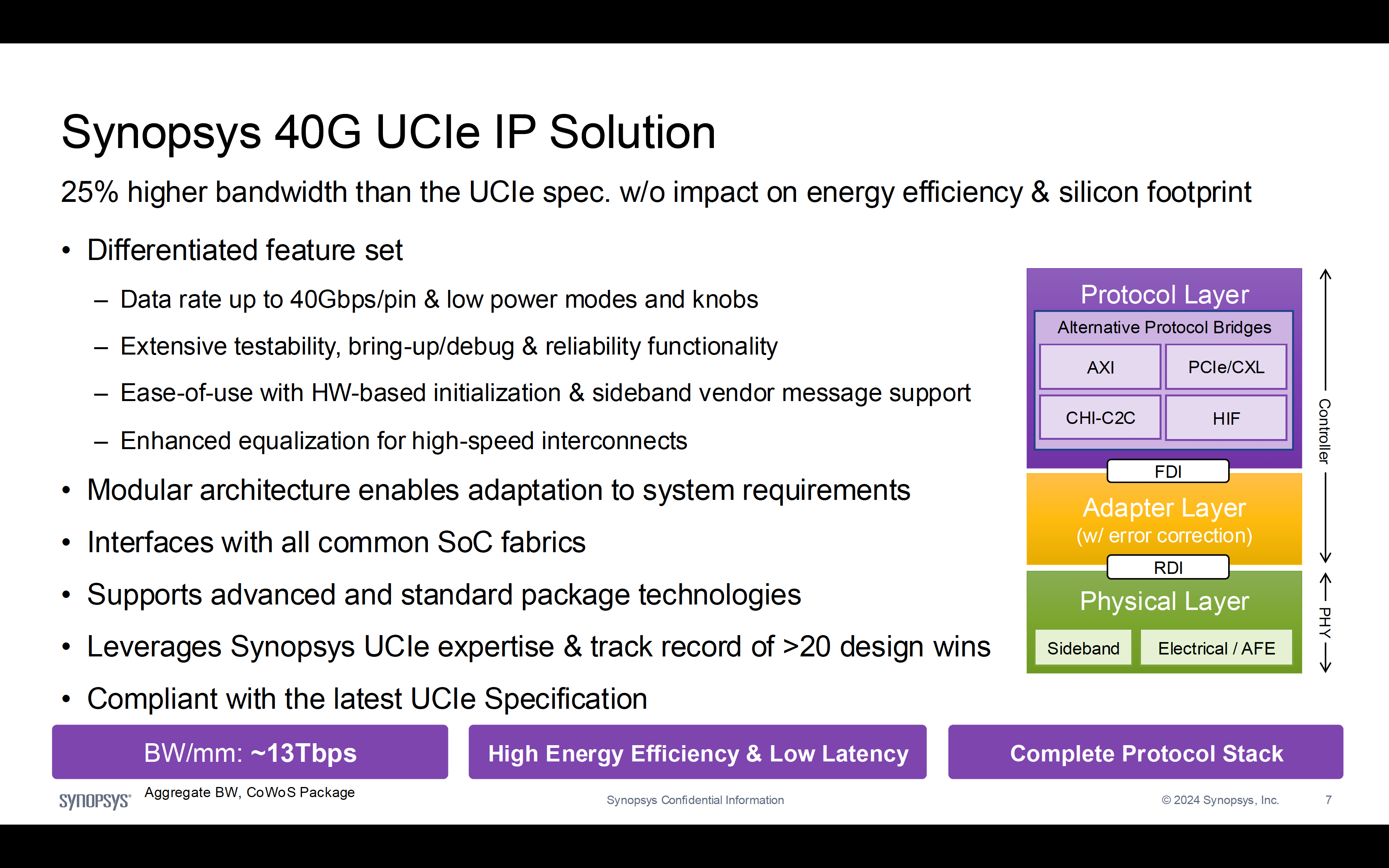

Andes Technology is Expanding RISC-V’s Horizons in High-Performance Computing ApplicationsBy: Dr. Charlie Su, President and CTO, Andes…Read More Synopsys Powers World’s Fastest UCIe-Based Multi-Die Designs with New IP Operating at 40 GbpsAs the demand for higher performance computing solutions…Read More

Synopsys Powers World’s Fastest UCIe-Based Multi-Die Designs with New IP Operating at 40 GbpsAs the demand for higher performance computing solutions…Read More PQShield Builds the First-Ever Post-Quantum Cryptography ChipQuantum computing promises to deliver vast increases in…Read More

PQShield Builds the First-Ever Post-Quantum Cryptography ChipQuantum computing promises to deliver vast increases in…Read MoreIntel Direct Connect Event

On Wednesday, February 21st Intel held their first Foundry Direct Connect event. The event had both public and NDA sessions, and I was in both. In this article I will summarize what I learned (that is not covered by NDA) about Intel’s business, process, and wafer fab plans (my focus is process technology and wafer fabs).

Business

… Read MorePodcast EP209: Putting Soitec’s Innovative Substrates to Work in Mainstream Products with Dr. Christophe Maleville

Dan is joined by Dr. Christophe Maleville, chief technology officer of Soitec’s Innovation. He joined Soitec in 1993 and was a driving force behind the company’s joint research activities with CEA-Leti. For several years, he led new SOI process development, oversaw SOI technology transfer from R&D to production and managed… Read More

A Candid Chat with Sean Redmond About ChipStart in the UK

When I first saw the Silicon Catalyst business plan 10 years ago I had very high hopes. Silicon Valley design starts were falling and Venture Capital Firms were distracted by software companies even though without silicon there would be no software.

Silicon Catalyst is an organization focused on accelerating silicon-based startups.… Read More

Achieving Extreme Low Power with Synopsys Foundation IP Memory Compilers and Logic Libraries

The relentless demand for lower power SoCs is evident across many markets. Examples include cutting-edge mobile, IoT, and wearable devices along with the high compute demands for AI and 5G/6G communications. Drivers for low power include battery life, thermal management and, for high compute applications, the overall cost… Read More

Navigating the 1.6Tbps Era: Electro-Optical Interconnects and 224G Links

In the relentless pursuit of ever-increasing data speeds, the 1.6 Terabits per second (Tbps) era looms on the horizon, promising unprecedented levels of connectivity and bandwidth within data centers. As data-intensive applications proliferate and the demand for real-time processing escalates, the need for robust and efficient… Read More

Arm Neoverse Continues to Claim Territory in Infrastructure

After owning general purpose compute in cell phones and IoT devices, it wasn’t clear what Arm’s next act might be. Seemingly the x86 giants dominated in datacenters and auguries suggested a bloody war in smaller platforms between Arm and RISC-V. But Arm knew what they were doing all along, growing upwards into infrastructure:… Read More

Pinning Down an EUV Resist’s Resolution vs. Throughput

The majority of EUV production is on 5nm and 3nm node, implemented by late 2022. Metal oxide resists have not been brought into volume production yet [1,2], meaning that only organic chemically amplified resists (CARs) have been used instead until now. These resists have a typical absorption coefficient of 5/um [3,4], which means

Cadence Debuts Celsius Studio for In-Design Thermal Optimization

Continuing the multiphysics theme, I talked recently with Melika Roshandell (Product Management Director at Cadence) on the continuing convergence between MCAD and ECAD. You should know first that Melika has a PhD in mechanical engineering and an extensive background in thermal engineering at Broadcom and Qualcomm, all very… Read More

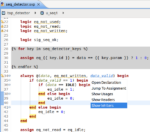

Handling Preprocessed Files in a Hardware IDE

For several years now, I’ve been meeting with AMIQ EDA co-founder Cristian Amitroaie every few months to discuss the state of the industry, key trends in design and verification, and the ways that they help facilitate and accelerate chip development. I noticed an interesting new feature mentioned in their latest press release… Read More

5 Expectations for the Memory Markets in 2025