I haven’t traveled a lot during the COVID-19 pandemic, but I have flown a few times around the U.S. As a former frequent flyer I pride myself on anticipating most travel circumstances and not being surprised or blindsided, but two recent visits to Austin, Texas, changed that when I couldn’t find a rental car.

It was just 12 months … Read More

You might have heard of the Multicore and Multiprocessor SoC (MPSoC) Forum sponsored by IEEE and other industry associations and companies. This group of top-notch academic and industry technical leaders gets together once a year to talk about hardware and software architecture and applications for multicore and multiprocessor… Read More

Taiwan and Korea represented 43% and 44% respectively with China at 15% and Japan and the US in the far distance.

ASML a tidal wave of orders

On the call management talked about logic potentially being up 30% in 2021 and memory being up potentially 50%. While we thing foundry/logic will clearly be on fir we think memory will lag a bit.… Read More

Agile methods in hardware design are becoming topical again. What does this mean for verification? Paul Cunningham (GM, Verification at Cadence) and I continue our series on research ideas. We’re also honored this month to welcome Raúl Camposano to our blog as a very distinguished replacement for Jim Hogan. As always, feedback… Read More

I read the semiconductor press, LinkedIn and social media (Twitter, Facebook) every morning along with an RSS feed that I setup, staying current on everything related to using EDA tools to make the task of SoC design a bit easier for design teams. A recent press release announced a tool called SoC Compiler, so my curiosity was piqued… Read More

PCI-SIG has held to doubling PCIe’s data rate with each revision of the specification. The consortium of 800 companies, with its board consisting of Agilent, AMD, Dell, HP, Intel, Synopsys, NVIDIA, and Qualcomm, is continuing this trend with the PCIe 6.0 specification which calls for a transfer rate of 64 GT/s. PCI-SIG released… Read More

-The semiconductor industry is not to blame its the customers

-How do you fix something that’s not really broken?

-Long taken for granted, semi’s are sexy again

-Pawns in a Political Power Play?

Its not the chip makers that screwed up. It’s the customers that stressed the system beyond breaking

The semiconductor… Read More

Mad scientists have been a staple of Hollywood science fiction since Dr Victor Frankenstein created his eponymous monster in 1931. Pre-pandemic, the Marvel Cinematic Universe was the main source of on-screen geeks-turned-superheroes, from Iron Man’s Tony Stark to Ant Man’s Hank Pym.

When it comes to real-life scientists on… Read More

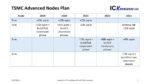

TSMC recently announced plans to spend $100 billion dollars over three years on capital. For 2021 they announced $30B in total capital with 80% on advanced nodes (7nm and smaller), 10% on packaging and masks and 10% on “specialty”.

If we take a guess at the capital for each year, we can project something like $30B for 2021 (announced),… Read More

Dan and Mike are joined by semiconductor and EDA executive Jack Harding. Jack has a diverse career as a technology executive beginning at IBM with notable stops along the way, including taking Cooper and Chyan Technology public, taking the helm from Joe Costello as CEO of Cadence and most recently as the founding CEO of eSilicon,… Read More

Is Intel About to Take Flight?