A few months ago, SemiWiki published an interview of Mike Wishart, CEO of Efabless. That interview provided insights into Efabless vision and its platform strategy. If you haven’t already read that post, please refer to it for background details. In essence, Efabless is about democratization of chip design and manufacturing.… Read More

RVA23 Ends Speculation’s Monopoly in RISC-V CPUsRVA23 marks a turning point in how mainstream…Read More

RVA23 Ends Speculation’s Monopoly in RISC-V CPUsRVA23 marks a turning point in how mainstream…Read More Perforce and Siemens Collaborate on 3DIC Design at the Chiplet SummitThe recent Chiplet Summit at the Santa Clara…Read More

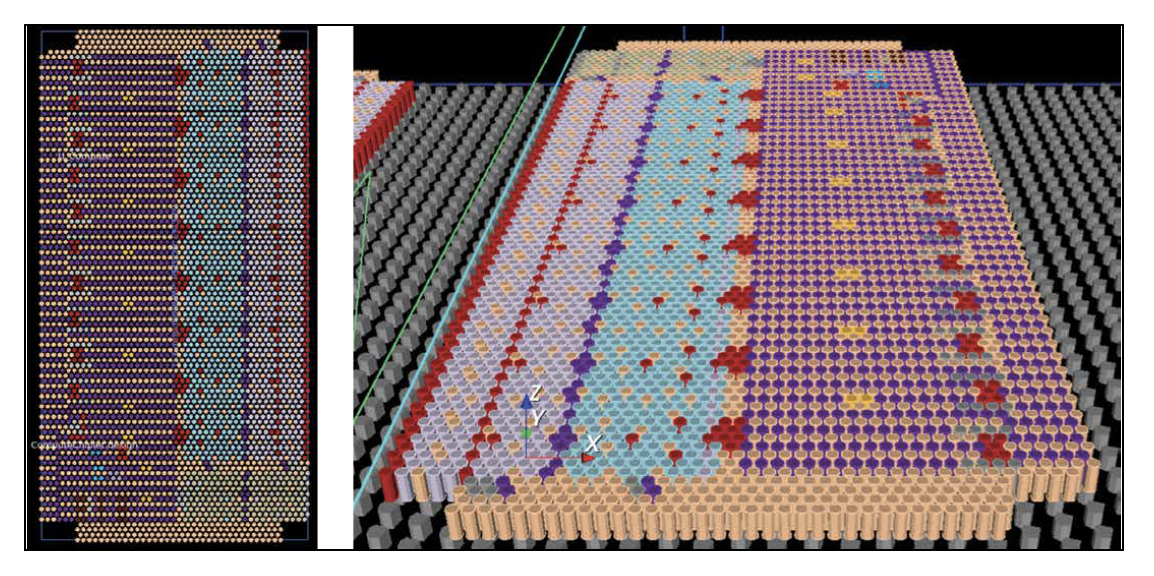

Perforce and Siemens Collaborate on 3DIC Design at the Chiplet SummitThe recent Chiplet Summit at the Santa Clara…Read More Building the Interconnect Foundation: Bump and TSV Planning for Multi-Die SystemsThe first article in this series examined how…Read More

Building the Interconnect Foundation: Bump and TSV Planning for Multi-Die SystemsThe first article in this series examined how…Read More CHERI: Hardware-Enforced Capability Architecture for Systematic Memory SafetyThe rapid escalation of cyberattacks over the past…Read More

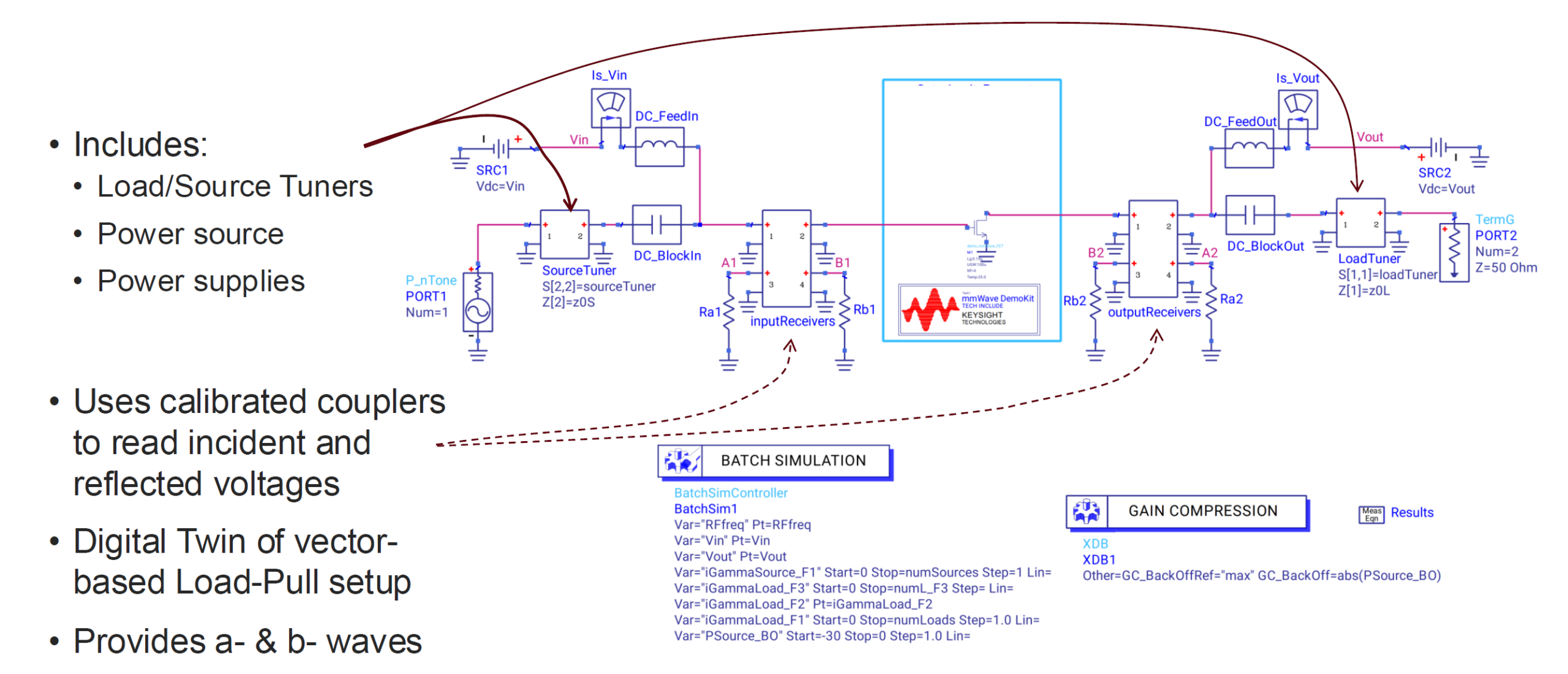

CHERI: Hardware-Enforced Capability Architecture for Systematic Memory SafetyThe rapid escalation of cyberattacks over the past…Read More WEBINAR: Two-Part Series on RF Power Amplifier DesignAt lower frequencies with simpler modulation, RF power…Read More

WEBINAR: Two-Part Series on RF Power Amplifier DesignAt lower frequencies with simpler modulation, RF power…Read MoreTechnology Design Co-Optimization for STT-MRAM

Previous SemiWiki articles have described the evolution of embedded non-volatile memory (eNVM) IP from (charge-based) eFlash technology to alternative (resistive) bitcell devices. (link, link)

The applications for eNVM are vast, and growing. For example, microcontrollers (MCUs) integrate non-volatile memory for … Read More

Demand for High Speed Drives 200G Modulation Standards

Right now, the most prevalent generation of Ethernet for data centers is 400 Gbps, with the shift to 800 Gbps coming rapidly. It is expected that by 2025 there will be 25 million units of 800 Gbps shipped. Line speeds of 100G are used predominantly for 400 Gbps Ethernet – requiring 4 lanes each. Initially 800 Gbps will simply … Read More

Advanced 2.5D/3D Packaging Roadmap

Frequent SemiWiki readers are no doubt familiar with the advances in packaging technology introduced over the past decade. At the recent International Electron Devices Meeting (IEDM) in San Francisco, TSMC gave an insightful presentation sharing their vision for packaging roadmap goals and challenges, to address the growing… Read More

Webinar: AMS, RF and Digital Full Custom IC Designs need Circuit Sizing

My career started out by designing DRAM circuits at Intel, and we manually sized every transistor in the entire design to get the optimum performance, power and area. Yes, it was time consuming, required lots of SPICE iterations and was a bit error prone. Thank goodness times have changed, and circuit designers can work smarter … Read More

White Paper: A Closer Look at Aging on Clock Networks

We all know that designers work hard to reach design closure on SOC designs. However, what gets less attention from consumers is the effort that goes into ensuring that these chips will be fully operational and meeting timing specs over their projected lifetime. Of course, this is less important for chips used in devices with projected… Read More

Podcast EP55: A New Year’s Perspective with Dan and Mike

Dan and Mike take some time to review 2021 – the events that led to growth, opportunities and challenges and a discussion of what lies ahead.

The views, thoughts, and opinions expressed in these podcasts belong solely to the speaker, and not to the speaker’s employer, organization, committee or any other group or individual.… Read More

DAC 2021 – Cliosoft Overview

It’s been awhile since I really looked at what Cliosoft has to offer in the EDA tool space, so at the 58th DAC I stopped by their exhibit booth on Tuesday to visit with Karim Khalfan, VP of Application Engineering, and Simon Rance, VP of Marketing. Their booth had all of the hot market segments listed: Automotive, 5G, IoT, AI, … Read More

Heterogeneous Integration – A Cost Analysis

Heterogeneous integration (HI) is a general term used to represent the diverse possibilities for die technology incorporated into advanced 2.5D/3D packaging. At the recent International Electron Devices Meeting (IEDM) in San Francisco, a team from Synopsys and IC Knowledge presented data from analyses of future potential… Read More

2D NoC Based FPGAs Valuable for SmartNIC Implementation

Smart network interface cards (SmartNICs) have proven themselves valuable in improving network efficiency. According to Scott Schweitzer, senior product manager at Achronix, it has been shown that SmartNICs can relieve up to – and perhaps beyond – 30% of the host processor’s loading. SmartNICs started out taking… Read More

CEO Interview with Jerome Paye of TAU Systems