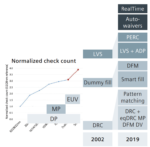

Electronic design automation (EDA) has come a long way from its beginnings. It has enabled chip engineers from specifying designs directly in layout format during the early days to today’s capture in RTL format. Every advance in EDA has made the task of designing a chip easier and increased the design team productivity, enabling… Read More

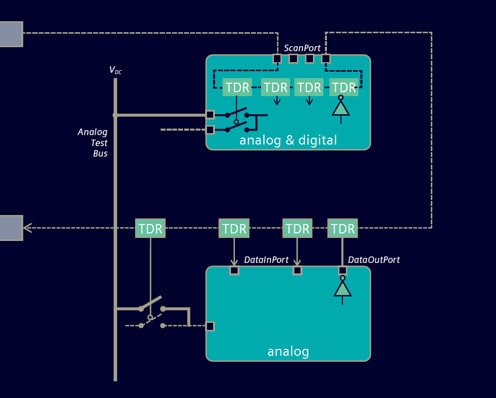

Something New in Analog Test AutomationDigital design engineers have used DFT automation technologies…Read More

Something New in Analog Test AutomationDigital design engineers have used DFT automation technologies…Read More MediaTek Develops Chip Utilizing TSMC’s 2nm Process, Achieving Milestones in Performance and Power EfficiencyMediaTek’s first chipset using 2nm technology expected in…Read More

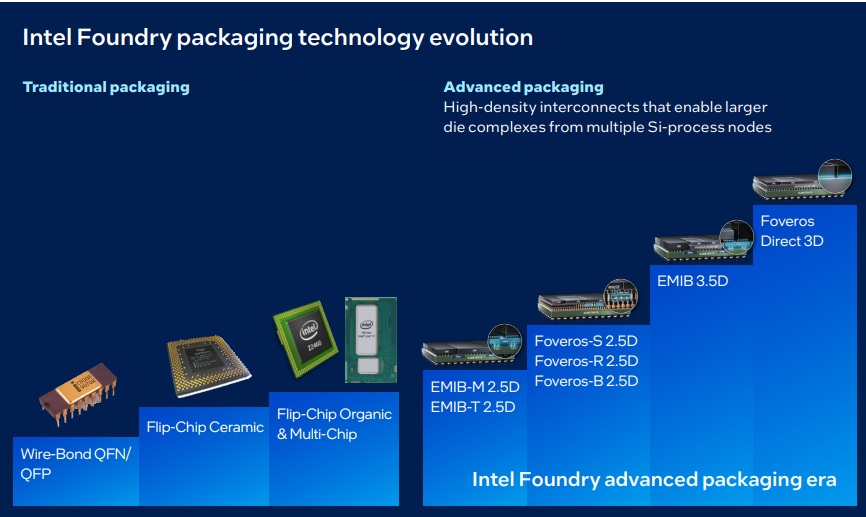

MediaTek Develops Chip Utilizing TSMC’s 2nm Process, Achieving Milestones in Performance and Power EfficiencyMediaTek’s first chipset using 2nm technology expected in…Read More Advancing Semiconductor Design: Intel's Foveros 2.5D Packaging TechnologyIn the rapidly evolving landscape of semiconductor manufacturing,…Read More

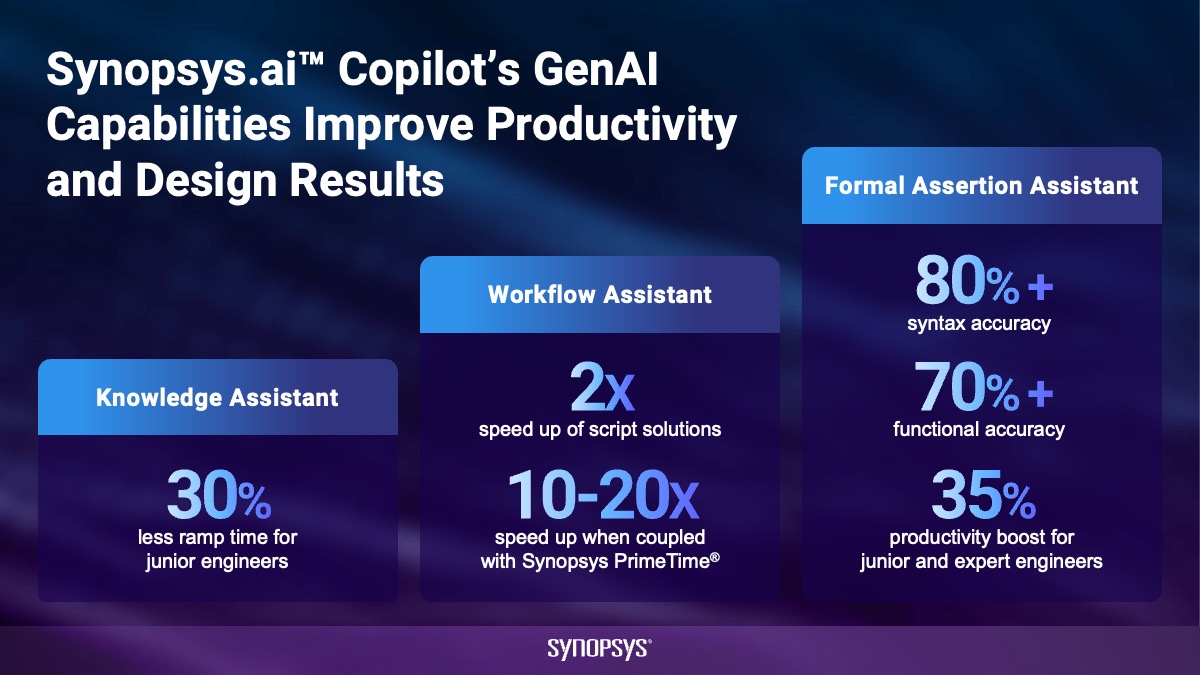

Advancing Semiconductor Design: Intel's Foveros 2.5D Packaging TechnologyIn the rapidly evolving landscape of semiconductor manufacturing,…Read More Synopsys Announces Expanding AI Capabilities and EDA AI LeadershipIn the fast-paced semiconductor industry Synopsys has redefined…Read More

Synopsys Announces Expanding AI Capabilities and EDA AI LeadershipIn the fast-paced semiconductor industry Synopsys has redefined…Read MoreSoC Vulnerabilities

As I read both the popular and technical press each week I often see articles about computer systems being hacked, and here’s just a few vulnerabilities from this week:

- Global phone hacks expose darker side of Israel’s startup nation image

- How Taiwan is trying to defend against a cyber World War III

- Kaseya receives

Optimize RTL and Software with Fast Power Verification Results for Billion-Gate Designs

In every chip, power is a progressive problem to be solved. Designers have long had to rely on a combination of experience and knowledge to tackle this dilemma, typically having to wait until after silicon availability to perform power analysis with realistic software workloads. However, this is too late in the game, as it becomes… Read More

Instrumenting Post-Silicon Validation. Innovation in Verification

Instrumenting post-silicon validation is not a new idea but here’s a twist. Using (pre-silicon) emulation to choose debug observation structures to instrument in-silicon. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO) and I continue our series on research… Read More

EDA in the Cloud – Now More Than Ever

A decade ago, many of us heard commentaries on how entrepreneurs were turned down by venture capitalists for not including a cloud strategy in their business plan, no matter what the core business was. Humorous punchlines such as, “It’s cloudy without any clouds” and “Add some cloud to your strategy and your future will be bright… Read More

Intel Accelerated

Intel presented yesterday on their plans for process technology and packaging over the next several years. This was the most detailed roadmap Intel has ever laid out. In this write up I will analyze Intel’s process announcement and how they match up with their competitors.

10nm Super Fin (SF)

10nm is now in volume production in three… Read More

Ansys Multiphysics Platform

Background

Traditionally, the interface between chip designers and system power, packaging, reliability, and mechanical engineering teams was a relatively straightforward exchange of specifications. Chip designers developed preliminary power dissipation estimates, often based on a simplifying power/mm**2 value. … Read More

WEBINAR: Architecture Exploration of System-on-chip using VisualSim Hybrid RISC-V and ARM Processor library

80% of specification optimization and almost 100% of the performance/power trade-offs can be achieved during architecture exploration of product design. RISC-V offers a huge opportunity with lots of pipeline and instruction set enhancement opportunities. Can it really attain the utopian success that people are looking… Read More

GM on BARRA’d Time

Midway through her seventh year running General Motors it’s time to assess the legacy of CEO and Chairperson Mary Barra, the first woman to run an automobile company. Of the 14 CEOs that have led GM, Barra’s term in office has been exceeded by only four of her predecessors: Alfred Sloan Jr. (May 10, 1923 – June 3, 1946), Roger

ASML- A Semiconductor Market Leader-Strong Demand Across all Products/Markets

– Strong demand across logic/memory & leading/trailing edge

– Customers want units fast-no time to test

– The main question is can ASML ramp to meet demand?

Revenue & Earnings low due to systems being rushed to customers

ASML reported Euro 4B in sales and Euro 1B in net income which while within guidance… Read More

Weebit Nano Moves into the Mainstream with Customer Adoption