We are all familiar with the tradeoffs between copper and fiber for digital signal transmission. The short version is that fiber is flexible, like copper but supports higher data rates with less loss over longer distances. The bad news is that converting digital signals to light and back again isn’t a trivial process. These kinds… Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read MoreBluetooth Based Positioning, More Accurate, More Reliable, Safer

Using Bluetooth for positioning is a topic I have touched on before, for location services, keyless entry, and asset tracking among other applications. Earlier implementations depended on measures of received signal strength and angle-of-arrival / angle-of-departure, but these have limited accuracy in environments with… Read More

How Intel, Samsung and TSMC are Changing the World

Given the changes in the music business, the term “Rock Star” doesn’t really have any relevance to music or its performers anymore. Instead, we use the term to describe leaders, innovators and generally people or organizations of great significance. In the world of semiconductors, the designers of advanced chips were the rock… Read More

Enhanced Stochastic Imaging in High-NA EUV Lithography

High-NA EUV lithography is the anticipated new lithography technology to be introduced for the 2nm node. Essentially, it replaces the 0.33 numerical aperture of current EUV systems with a higher 0.55 numerical aperture (NA). This allows the projection of smaller spot sizes and smaller pitches, roughly 60% smaller compared … Read More

How Philips Saved TSMC

TSMC and Philips have deep historical ties. In fact, TSMC may not have existed without Philips. In the 1980s TSMC was established as a joint venture with Philips Electronics, the government of Taiwan, and other private investors. Several semiconductor companies were approached by Morris Chang for funding including semiconductor… Read More

EP177: The Certus Approach to Meeting the Challenges of I/O and ESD with Stephen Fairbanks

Dan is joined by Stephen Fairbanks, CEO of Certus Semiconductor. Stephen is an ESD pioneer with over 30 years of experience starting with his time at Intel, SRF Technologies, and now Certus Semiconductor.

Stephen describes the varied challenges of ESD andI/O library design presented by today’s technologies and design… Read More

CEO Interview: Anna Fontanelli of MZ Technologies

Anna has more than 25 years of expertise in managing complex R&D organizations and programs, giving birth to a number of innovative EDA technologies. She has pioneered the study and development of several generations of IC and package co-design environments and has held senior positions at leading semiconductor and EDA … Read More

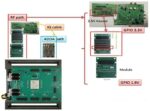

Sirius Wireless Partners with S2C on Wi-Fi6/BT RF IP Verification System for Finer Chip Design

Sirius Wireless, a provider of RF IP solutions, collaborated with FPGA prototyping solutions expert S2C to develop its Wi-Fi6/BT RF IP Verification System, aiming to improve work efficiency and reduce time-to-market for their clients.

The emergence of Wi-Fi6, a wireless connection technology (WCT), has unleashed unexpected… Read More

How Do You Future-Proof Security?

If you are designing electronics to go into a satellite or a military drone, it better have a useful lifetime of 15-20 years or more. Ditto for the grid or other critical infrastructure, your car, medical devices, anything where we demand absolute reliability. Reliability also requires countermeasures against hacking by anyone… Read More

LIVE WEBINAR: Accelerating Compute-Bound Algorithms with Andes Custom Extensions (ACE) and Flex Logix Embedded FPGA Array

RISC-V have great adoption and momentum. One of the key benefits of RISC-V is the ability for SoC designers to extend its instruction sets to accelerate specific algorithms. Andes’ ACE (Andes Custom Extensions) allow customers to quickly create, prototype, validate and ultimately implement custom memories, dedicated ports… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!