Could this be more bad news for semicap spend? Negative for US chip independence & AMD costs ? Rumors of Global Foundries dropping out of the 7NM race have been increasing rapidly. What could be a fatal blow to the GloFo 7NM program was AMD deciding to go with TSMC for 7NM first for one product and finally for its next generation CPUs.… Read More

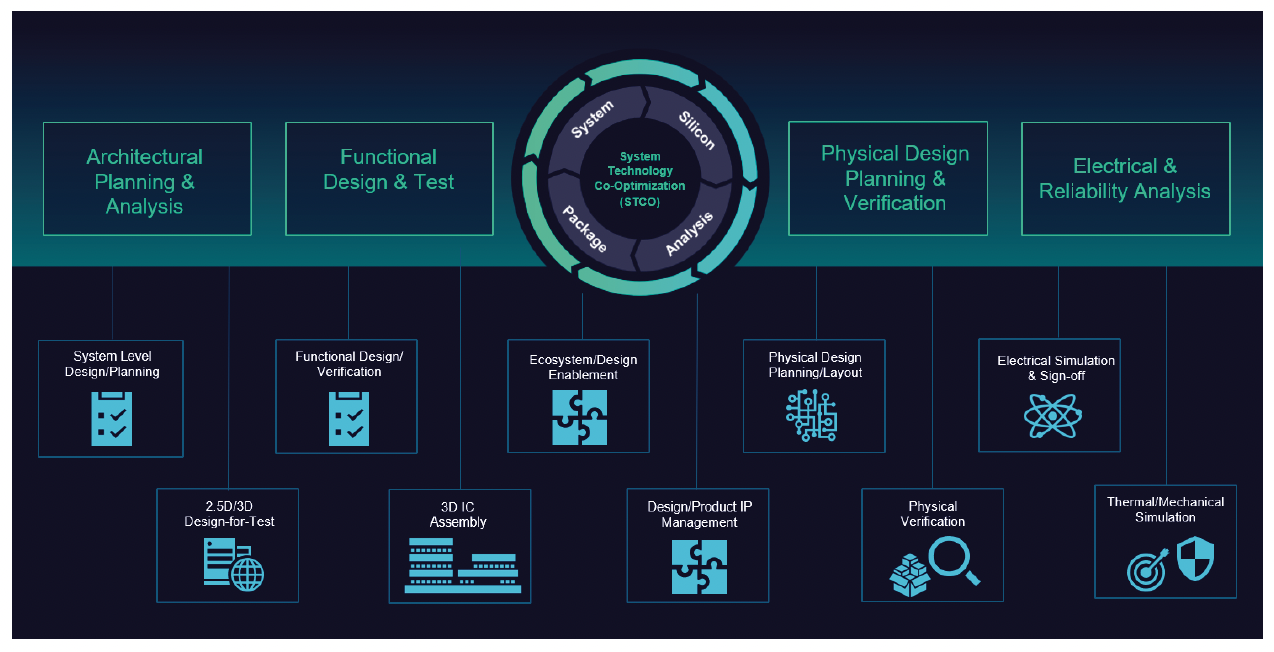

Enabling the Ecosystem for True Heterogeneous 3D IC DesignsThe demand for higher performance, greater configurability, and…Read More

Enabling the Ecosystem for True Heterogeneous 3D IC DesignsThe demand for higher performance, greater configurability, and…Read More Why I Think Intel 3.0 Will SucceedProbably one of the most anticipated semiconductor investor…Read More

Why I Think Intel 3.0 Will SucceedProbably one of the most anticipated semiconductor investor…Read More Griffin Securities’ Jay Vleeschhouwer on EDA Acquisitions and StartupsJay Vleeschhouwer, Managing Director of Software Research at…Read More

Griffin Securities’ Jay Vleeschhouwer on EDA Acquisitions and StartupsJay Vleeschhouwer, Managing Director of Software Research at…Read More Security Coverage: Assuring Comprehensive Security in Hardware DesignAs hardware systems become increasingly complex and security…Read More

Security Coverage: Assuring Comprehensive Security in Hardware DesignAs hardware systems become increasingly complex and security…Read More Scaling 3D IC Technologies – Siemens Hosts a Meeting of the Minds at DAC3D IC was a very popular topic at…Read More

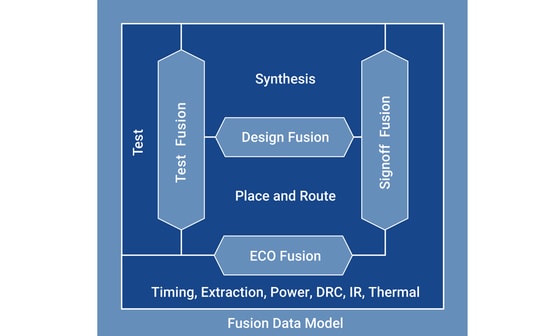

Scaling 3D IC Technologies – Siemens Hosts a Meeting of the Minds at DAC3D IC was a very popular topic at…Read MoreA Closer Look at Fusion from Synopsys at #55DAC

Synopsys is pretty well-known for their early entry into logic synthesis with the Design Compiler tool and more recent P&R tool with IC Compiler, so I met up with two folks at DAC to get a better idea of what this new Fusion technology was all about where the barriers between tools are changing. Michael Jackson and Rahul Deokar … Read More

How Design Can Make Tech Products Less Addictive

It’s the summer of 2018, the summer of Fortnite, and we all know we are addicted. Addicted to email, Snapchat, Instagram, Fortnite, Facebook. We swap outdoor time on the trail for indoor time around the console. Our kids log into Snapchat every day on vacation to keep their streaks alive and then get lost in the stream.

We move less … Read More

Improving Yield and Reliability with In-Chip Monitoring, there’s an IP for that

There’s an old maxim that you can only improve what you measure, so quality experts have been talking about this concept for decades and our semiconductor industry has been the recipient of such practices to such an extent that we can now buy consumer products that include chips with over 5 billion transistors in them. You’ve… Read More

Semiconductors Become a Worldwide Business

This is the twelfth in the series of “20 Questions with Wally Rhines”

Among the companies that bought a license from AT&T to produce the transistor was Sony. While the U.S. maintained its lead in technology, other countries like Japan emerged as competitors. Semiconductor manufacturing was both labor intensive… Read More

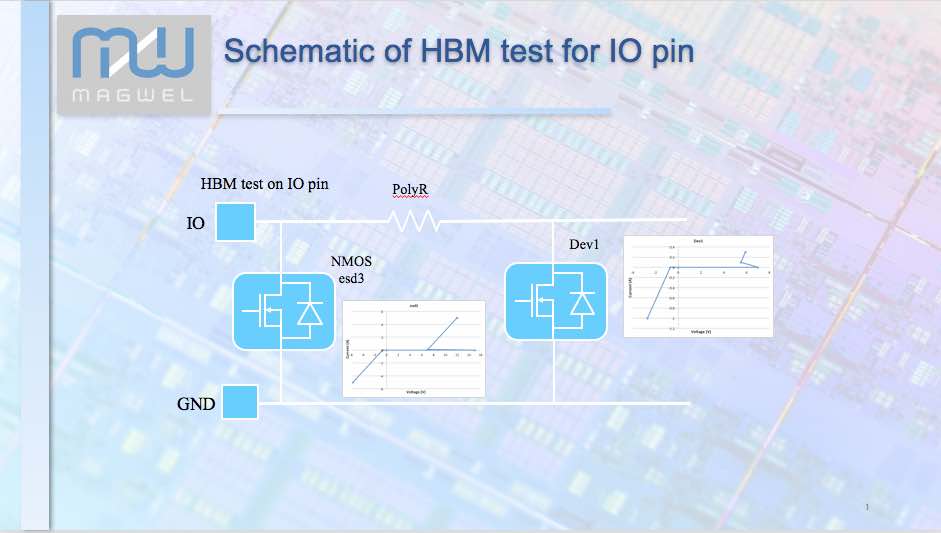

Verifying ESD Fixes Faster with Incremental Analysis

The author of this article, Dündar Dumlugöl, is CEO of Magwel. He has 25 years of experience in EDA managing the development of leading products used for circuit simulation and high-level system design.

Every designer knows how tedious it can be to shuttle back and forth between their layout tool and analysis tools. Every time an… Read More

Webinar: Ensuring System-level Security based on a Hardware Root of Trust

A root of trust, particularly a hardware root of trust, has become a central principle in well-architected design for security. The idea is that higher layers in the stack, from drivers and OS up to applications and the network, must trust lower layers. What does it help it to build great security into a layer if it can be undermined… Read More

When it Comes to Process Migration, “Standard Cells” are Anything But

Standard cell library developers are faced with a daunting task when it is time to create a library for a new process node. Porting an existing library can be a big help, but even then, manual modifications to 800 or more cells is still required. Each of those cells has many geometric elements are that affected by new design rules. All… Read More

The Pain of Test Pattern Bring-up for First Silicon Debug

In the semiconductor world we have divided our engineering talent up into many adjacent disciplines and each comes with their own job titles: Design engineers, Verification engineers, DFT engineers, Test engineers. When first silicon becomes available then everyone on the team, and especially management all have a few big … Read More

Harnessing Clock and Power

Switching translates to power. Similar to the recent slow down experienced by Moore’s Law, the constant power density (power demand per unit chip area) prescribed by Dennard scaling was no longer affordable across the technological scaling. While the contribution of leakage power component in advanced process nodes was getting… Read More

Musk’s new job as Samsung Fab Manager – Can he disrupt chip making? Intel outside