Synopsys is pretty well-known for their early entry into logic synthesis with the Design Compiler tool and more recent P&R tool with IC Compiler, so I met up with two folks at DAC to get a better idea of what this new Fusion technology was all about where the barriers between tools are changing. Michael Jackson and Rahul Deokar of Synopsys arrived on time in the press area of DAC to chat about Fusion. Historically the EDA industry has used lots of separate databases and data models, engines and fragmented flows, but now we have Fusion technology:

I did a Q&A session to get to the gist of things:

L: Rahul Deokar, Product Management and Business Development Director, Design Group

R: Michael Jackson, Corporate VP of Marketing and Business Development, Design Group

Q: What are the big benefits of using Fusion?

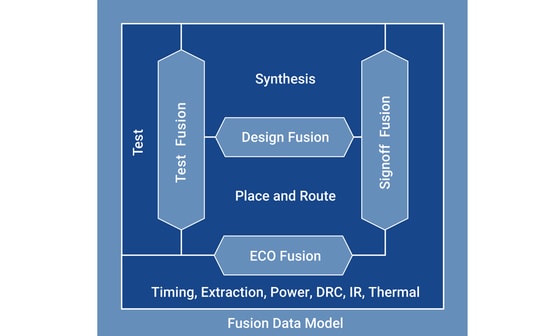

Fusion Technology redefines conventional EDA tool boundaries across synthesis, place-and-route and signoff, sharing engines across the industry’s premier digital design tools, and using a unique, single data model for both logical and physical representation.

Fusion enables better QoR with unified physical synthesis across front-end design and place-and-route. It facilitates synthesis technology QoR inside place-and-route, and place-and-route QoR inside synthesis. The re-synthesis optimization capability provides synthesis-based logic restructuring for area and leakage power recovery during place-and-route. This fast re-synthesis in critical regions results in significantly improved QoR and faster convergence.

Fusion also provides PrimeTime’s accurate path-based analysis (PBA)-driven optimization in place-and-route for the best QoR closure. Using fast and efficient PBA eliminates unnecessary margins and thousands of spurious violating paths. Surgical place-and-route changes are made to meet signoff requirements, eliminating the need for changes to unaffected parts of the circuit. Fewer paths to fix for timing allows more paths for power and area recovery, resulting in fewer buffers, fewer low-VT cells, and lower power.

Essentially, Fusion enables designers to accelerate the delivery of their designs with industry-best full-flow quality-of-results (QoR) and the fastest time-to-results (TTR).

Q: Why would Synopsys develop a new data model?

Market and technology drivers are forcing a transformation of the traditional RTL-to-GDSII design flow. In the past, designers put together their own flows by cobbling together a set of disconnected tools from different vendors with clear lines of demarcation between the major phases of the design flow: Synthesis, Place-and-Route, Signoff. These functional boundaries inevitably cause major rework due to associated hiccups when transitioning from one design phase to the next. This makes for non-linear, non-monotonic, non-convergent progress that is far from optimal.

The Fusion Data Model is a single data model that fuses together both the logical and physical representations of the design. It enables one DNA backbone across the Synopsys Design Platform that includes IC Compiler™ II place-and-route, Design Compiler® Graphical synthesis, PrimeTime® signoff, StarRC™ extraction, IC Validator physical verification, DFTMAX™ test, TetraMAX® II automatic test pattern generation (ATPG), SpyGlass® DFT ADV RTL testability analysis and Formality® equivalence checking. It provides the same interpretation of rules and design intent throughout the flow, and is based on a shared massively-parallel and machine-learning ready infrastructure.

Q: Will competitor tools Calibre or Genus integrate with Fusion?

No, but you could still use the tools separately in a mixed flow.

Ansys does have a Fusion connection because they are more complimentary.Significant productivity improvements are realized through the application of Fusion in ANSYS RedHawk and IC Compiler II place-and-route solution enabling transparent data transfer between the place-and-route environment and power integrity analysis. The resulting productivity improvements are a result of eliminating scripting files and cumbersome flows which require external manipulation of data.

Related blog – Retooling Implementation for Hot Applications

Q: Can I keep using ICC1, or will I be forced to upgrade to ICC2?

Yes, you can keep using ICC1 with Milkyway as desired, however ICC2is built on the new Fusion Data Model that goes beyond Milkyway.

Q: Where is AI being used at Synopsys to make EDA tools smarter?

We have a Corporate level focus at Synopsys on AI that spans our Business Units and is manifested in enhanced EDA tools and IP. In June this year, Synopsys announced our AI-enhanced Digital Design Platform with state-of-the-art machine-learning capabilities to address the extreme complexities of leading-edge design. This is part of an ongoing, multi-year initiative with broadening investment in AI, alongside leading industry partners.

Our PrimeTime tool is using AI techniques for power recovery to get power ECO speed-ups. With PrimeTime the tool is actually trained at the customer site. As PrimeTime learns more transforms for power-savings then the runtimes get faster, from 4X to 10X better.

Our customer Renesas observed more than 4X power ECO speed-up over their existing production flow, while achieving the same timing and power QoR. They could complete ECO runs in hours versus the days it took before, and reuse learnings across blocks, hierarchies, and even design styles.

Q: How would a PrimeTime customer report a bug that could be replicated in the factory?

For bug replication the customer can send their encrypted learning and the netlist to the factory.

Q: How does a customer start using Fusion?

They would buy the tools in the Synopsys Design Platform, and get some training by local AEs to produce the best results.

Q: Does Fusion apply to FPGA design flows?

No, it targets IC design.

Q: Which customers are using Fusion these days?

Well, three months ago at SNUG we heard from: Samsung, Toshiba, ST, Ansys

Monday at DAC – AMD, Broadcom, Qualcomm, Renesas, Samsung, Vatics, Arm

Q: Which nodes is Fusion ready to work with?

Fusion will work at mature process nodes down to the most advanced being used today at 7nm, 5nm and 3nm.

Q: Will automotive IC designers benefit from Fusion?

Yes, Synopsys’ Design Platform is ISO26262 certified and Automotive customers such as Renesas have benefited from the application of Fusion in their designs.

Q: Does the IP group within Synopsys use Fusion?

Yes, our internal IP users are using Fusion, and the bigger the block the bigger the benefits.

Summary

I think that Synopsys has made another savvy transition in their technology direction with Fusion, having a common data model makes a lot of sense to me especially as design sizes increase and the interaction between tools increase to meet closure (timing, power, reliability, etc.), Early feedback from customers sounds hopeful, so now you just need to make that financial decision on upgrading or not.

Comments

There are no comments yet.

You must register or log in to view/post comments.