A Phase-Locked Loop (PLL) gives design a heartbeat. Despite its minute footprint, it has many purposes such as being part of the clock generation circuits, on-chip digital temperature sensor, process control monitoring in the scribe-line or as baseline circuitry to facilitate an effective measurement of the design’s power delivery network (PDN).

A Phase-Locked Loop (PLL) gives design a heartbeat. Despite its minute footprint, it has many purposes such as being part of the clock generation circuits, on-chip digital temperature sensor, process control monitoring in the scribe-line or as baseline circuitry to facilitate an effective measurement of the design’s power delivery network (PDN).

To most of us, its prevalent use is probably known as part of a frequency synthesizer –it controls proper clock sequencing and acts as basis for switching activities across the design. An ideal PLL has to satisfy several criteria including a low-jitter requirement, a low-phase-noise and high reliability.

Aside from some robust mixed signal design techniques, the physical characteristics of the underlying components captured in the simulation models have greatly influenced the overall PLL quality. Due to its importance and these stringent design requirements, PLL is hardly included as off-chip and is usually reworked for a design that is retargeted for different process node or for a significant frequency shift.

Silicon Creations is a privately held and global silicon IP provider focusing on precision and general-purpose timing PLLs, low power and high-performance SerDes, and high-speed differential I/Os. Its IPs cover across various process technologies. At the TSMC Open Innovation Platform held during DAC 2018 in San Francisco, Randy Caplan, EVP and Co-Founder of Silicon Creations, shared the state of his company products and the challenges that designers should be cognizant with as process technology is trending towards 5nm. The following notes are excerpted from his presentations and a subsequent 1-on-1 interview.

Silicon Creations is a privately held and global silicon IP provider focusing on precision and general-purpose timing PLLs, low power and high-performance SerDes, and high-speed differential I/Os. Its IPs cover across various process technologies. At the TSMC Open Innovation Platform held during DAC 2018 in San Francisco, Randy Caplan, EVP and Co-Founder of Silicon Creations, shared the state of his company products and the challenges that designers should be cognizant with as process technology is trending towards 5nm. The following notes are excerpted from his presentations and a subsequent 1-on-1 interview.

PLL

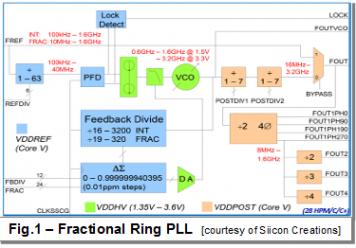

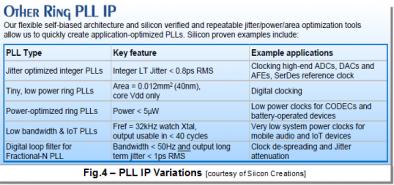

Successfully deployed to over 160 customers globally, Silicon Creation’s IPs (PLLs, oscillators and high-speed interface) have been core to over 500 tapeouts. Its mainstream PLL is the general purpose Fractional-N Ring PLL, which is dubbed as “One-Size-Fits-All” synthesizer. It is adequately flexible to reduce risk (<0.01 ppm frequency step) and has programmable power for jitter optimization (rating at <1mW and <5ps RMS long-term jitter). One of the attractive differentiating factors for this Fractional PLL compared with others is in providing programmability. It covers a wider range of power vs performance tradeoffs and is retargetable for many applications, hence lowering both the risk and the development cost.

Successfully deployed to over 160 customers globally, Silicon Creation’s IPs (PLLs, oscillators and high-speed interface) have been core to over 500 tapeouts. Its mainstream PLL is the general purpose Fractional-N Ring PLL, which is dubbed as “One-Size-Fits-All” synthesizer. It is adequately flexible to reduce risk (<0.01 ppm frequency step) and has programmable power for jitter optimization (rating at <1mW and <5ps RMS long-term jitter). One of the attractive differentiating factors for this Fractional PLL compared with others is in providing programmability. It covers a wider range of power vs performance tradeoffs and is retargetable for many applications, hence lowering both the risk and the development cost.

Challenges in Advanced Process Nodes

Reviewing technology progression from 180nm to 7nm and beyond as it applies to Silicon Creations products, it is apparent that analog does scale although at two order magnitude less than the digital scaling. The analog scaling has been closely tied to the circuit capacitance area as analog noise relates to kT/C.

Furthermore, the DRC increased complexity is true also for analog design as the inherent device customization tracks closely with the more stringent FinFET requirements. The complex 5nm DRC incurs longer simulation and physical verification time (an order of magnitude longer than those of 10nm process node), which leads to a higher development cost, longer development cycles and an increased of compute capacity.

The shift from a capacitive-centric parasitic element to a resistive dominant is more pronounced in 7nm and beyond. Hence, an accurate modeling or extraction of wire resistance is paramount in ensuring a proper analysis.

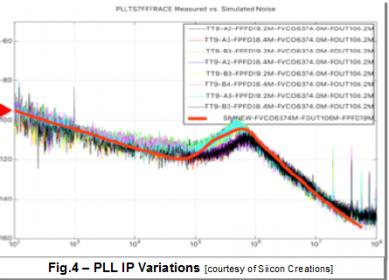

For the 7nm post-silicon related efforts, an excellent correlation was obtained between the simulated data versus the measured performance as shown in figure 2. The PLL power as a function of measured current was also demonstrated to be tightly aligned with the simulated values (at 3.02uA with 1.5% standard deviation).

For the 7nm post-silicon related efforts, an excellent correlation was obtained between the simulated data versus the measured performance as shown in figure 2. The PLL power as a function of measured current was also demonstrated to be tightly aligned with the simulated values (at 3.02uA with 1.5% standard deviation).

Randy final takeaways include a continued progress in his company product releases such as LVDS and SerDes interfaces to 25Gbps, and PLL’s successful production use in 7nm. Moreover, the lessons learned from earlier FinFET processes including 7nm can be leveraged to meet the increased requirements from 5nm –needing no new techniques. However, special attention is needed for parasitics, proximity and matching as well as balancing accuracy versus design time.

Here are selected notes taken from a subsequent Q&A session with Randy:

What types of challenges you faced with design trending towards 5G and automotives?

“Automotive particularly is pretty challenging. 5G is very specific niche business, with special PLL and special SerDes, so we haven’t plan a lot of options in that area,” Randy said. He mentioned that automotive is a huge new business and presents lot of new fundamental challenges such as addressing failure. “How do you know if something goes wrong. The only way to know is by using the other circuits to monitor the existing circuit,” he explained. A year ago the automotive standards was not well defined and has since evolving quite rapidly led by few leaders in this area such as Synopsys, Mentor and TSMC –helping to define the standards. He asserted that Silicon Creations is trying to comply with the evolving ecosystems including designing monitor circuits outside their IPs.

Most of your customers indicated that early integration work seems to play a major role in ensuring first silicon success?

Randy reaffirmed that for the advanced nodes such as 16nm and below, it is critical to always allocate time in the standard flow for a first silicon validation. “It is common also for 7nm and 5nm that some design iterations may be needed. Of this maybe the programming phase –it does not mean you have to change the hard macro… You may not know the optimal operating mode of your IP at that time,” he said.

He added that it is hard to break apart the IP itself to the fundamental components that might give insights into the process. Silicon Creations’ testchip has a PCM section which contains ring oscillator, individual devices, current mirror, noise analysis related circuitry, etc. intended for such correlation. He mentioned that in the end, when the PDK 1.0 is released, the process correlates with the simulation results as what was successfuly demonstrated with the 7nm process.

What make your product offering unique compared with others?

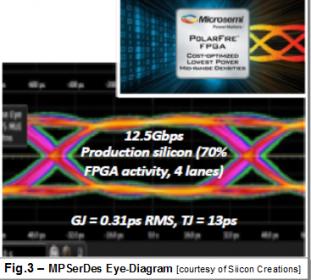

“On the SerDes side, we have very competitive PPA specifications. We use 16Gbps ring oscillator based PLL to support up to 30 different standards.” Randy said. He mentioned that the ring oscillator is differentiated from other designs that use inductor based, which incur more area and power. The sheer volume of its production proven PLL, a single architecture across process nodes, also helps customers to reduce the risk to their products It is used in over 500 chips in mass production to date.

“On the SerDes side, we have very competitive PPA specifications. We use 16Gbps ring oscillator based PLL to support up to 30 different standards.” Randy said. He mentioned that the ring oscillator is differentiated from other designs that use inductor based, which incur more area and power. The sheer volume of its production proven PLL, a single architecture across process nodes, also helps customers to reduce the risk to their products It is used in over 500 chips in mass production to date.

As ring oscillator is a common part of the foundry test circuits (such as TSMC) and is used for gauging a new process readiness, it is reassuring to learn that Silicon Creations PLL IP is well underway for 5nm.

Check HERE for a summary of SC’s products and HERE for more details.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.