The demand for high-bandwidth, low-latency networking solutions has never been greater. As artificial intelligence (AI) workloads continue to grow exponentially, and hyperscale data centers become the backbone of our digital infrastructure, the need for faster and more efficient communication technologies becomes imperative. 1.6T Ethernet will rapidly be replacing 400G and 800G Ethernet as the backbone of hyperscale data centers.

Hyperscale data centers, which power everything from cloud computing and big data analytics to AI and machine learning, require high-bandwidth, low-latency chips and interfaces to process petabytes of data quickly and efficiently. As the demand for computing power continues to grow, so does the energy consumption of data centers. High power consumption by interconnects leads to increased heat generation, which in turn requires more robust cooling systems to maintain optimal operating temperatures. By reducing interconnect power consumption, less heat is generated, overall energy efficiency can be improved, leading to cost savings and reduced environmental impact. In essence, when it comes to AI and data center infrastructure, it is the latency, power and size trifecta that are of critical importance, in addition to the speed.

Synopsys recently unveiled the industry’s first complete 1.6T Ethernet IP solution that addresses all of the above requirements. Enabling up to 40% latency reduction, 50% interconnect power reduction and 50% area reduction compared to existing solutions, Synopsys’ complete solution includes a pre-verified subsystem, giving a head start to chip designers.

Complete Solution

The complete 1.6T Ethernet IP solution from Synopsys includes a range of innovative technologies designed to optimize performance, reduce power consumption, and accelerate time-to-market for AI and HPC networking chips.

Following is a contextual quote from Mick Posner, VP of Product Management, High Performance Computing IP Solutions at Synopsys.

“The silicon providers behind data center units require adoption of the latest generation of interconnect protocols so that they can optimize their silicon to scale with new workloads. And this is exactly where 1.6 Ethernet comes in.”

Offering customers a complete Ethernet IP solution simplifies integration, reduces complexity, optimizes performance, eases deployment, provides consistent support, enables scalability, and helps mitigate risks. These benefits ultimately lead to greater customer satisfaction and success in deploying and maintaining Ethernet IP networks.

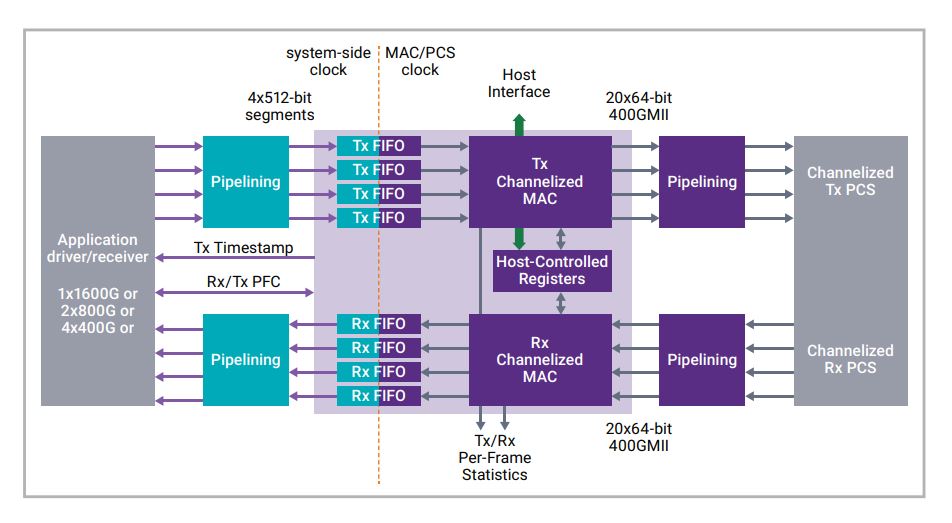

The Synopsys 1.6T Ethernet IP solution features new, optimized MAC and PCS IP

1.6T MAC and PCS Ethernet Controllers

Forward Error Correction (FEC) mechanisms play a pivotal role in enhancing the reliability of data transmission over high-speed links, particularly in the context of 1.6Tbps traffic. While FEC helps combat errors and ensures data integrity, its implementation introduces additional considerations such as area, power consumption and latency. Striking the right balance between Bit Error Rate (BER), power efficiency, and latency becomes imperative in designing efficient communication systems for the 1.6T era. By implementing a patented Reed-Solomon FEC architecture, Synopsys is able to decrease area by 50% and reduce latency by 40% on the 1.6T Ethernet MAC and multi-channel, multi-rate PCS Controllers without sacrificing reliability across Ethernet rates from 10G to 1.6T.

224G Ethernet PHY IP

Synopsys’ silicon-proven Ethernet PHY IP delivers robust link performance with exceptional signal integrity, supporting chip-to-chip, chip-to-module, and copper cable connections. The customizable PHY IP optimizes power and performance tradeoffs, providing seamless ecosystem interoperability for multiple channel lengths.

Verification IP

Synopsys’ verification IP for up to 1.6T Ethernet speeds accelerates time-to-market by speeding up the verification process. Implemented in native SystemVerilog and Universal Verification Methodology (UVM), the verification IP provides a comprehensive set of protocol, methodology, and productivity features, ensuring reliable and efficient testing of Ethernet designs. As the industry’s first Ethernet verification IP for up to 1.6T, it helps speed time to first test.

Backward Compatibility

Synopsys’ 1.6T IP solution is backward compatible with 400G and 800G Ethernet solutions, allowing users to upgrade or expand their systems at their own pace without facing costly disruptive changes. Backward compatibility is vital for preserving investments, ensuring smooth transitions, and promoting interoperability in software, hardware, and protocols. By allowing users to seamlessly integrate new technologies with existing systems, the Synopsys solution’s backward compatibility minimizes disruption and reduces the learning curve.

Silicon to Systems Design Solutions

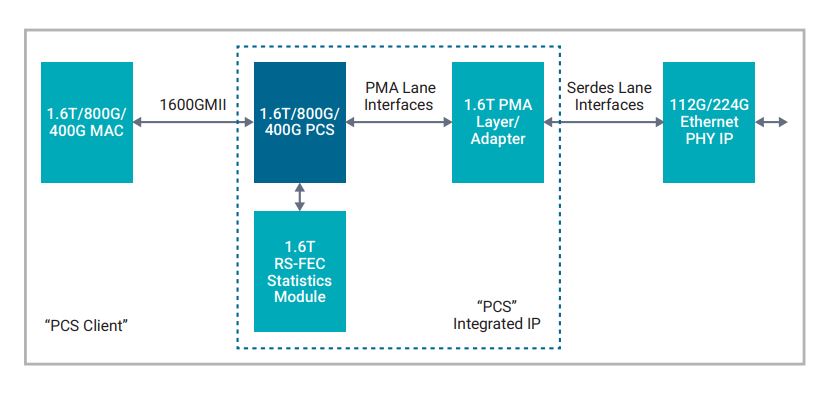

Synopsys’ complete solution includes pre-verified subsystems enabling customers to streamline their development process and reduce time-to-market and development risks. These subsystems, rigorously tested and validated by suppliers, ensure high reliability and adherence to industry standards. Equipped with these, customers can focus on their core competencies while enjoying scalability and flexibility. The accelerated time-to-market enhances the overall return on investment, making pre-verified subsystems a valuable asset for efficient product development by customers large, medium and small alike.

The Synopsys 1.6T Ethernet IP solution subsystem integrates pre-verified MAC, PCS, and PHY

Summary

Synopsys’ complete 1.6T Ethernet IP solution represents a significant milestone in the evolution of networking technologies for AI and hyperscale data centers. By offering innovative solutions that optimize performance, lower latency, reduce power consumption, and accelerate time-to-market, Synopsys is helping to drive the future of AI and high-performance computing, enabling customers to meet current and future demands of the most data-intensive workloads.

For more details, visit Synopsys Complete 1.6T Ethernet IP Solution.

You can access Synopsys’ press release on their complete 1.6T Ethernet IP solution here.

Also Read:

2024 Signal & Power Integrity SIG Event Summary

Navigating the 1.6Tbps Era: Electro-Optical Interconnects and 224G Links

Why Did Synopsys Really Acquire Ansys?

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.